## Heterogenous Package Thermal Characterization and Modeling

Unrestricted | © Siemens 2023 | Siemens Digital Industries Software

Introduction Thermal Transient Test approach

- Body diode

- I/O Pin

- TTV

**Structure Functions**

Application examples

Potential next steps

## Introduction

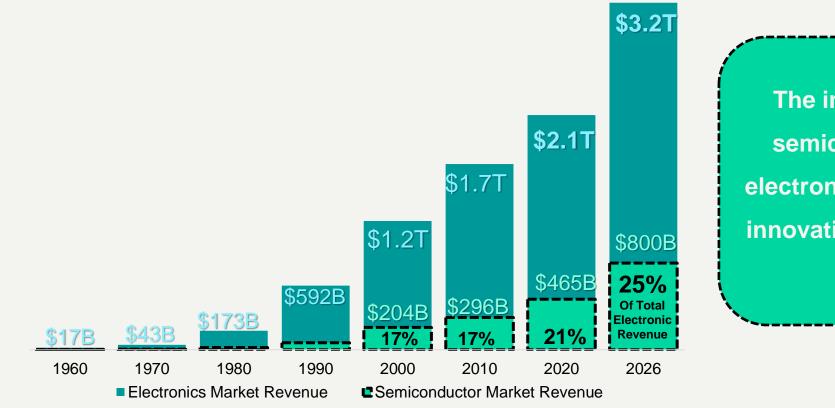

#### **Increasing Semiconductor Content in Electronics Systems**

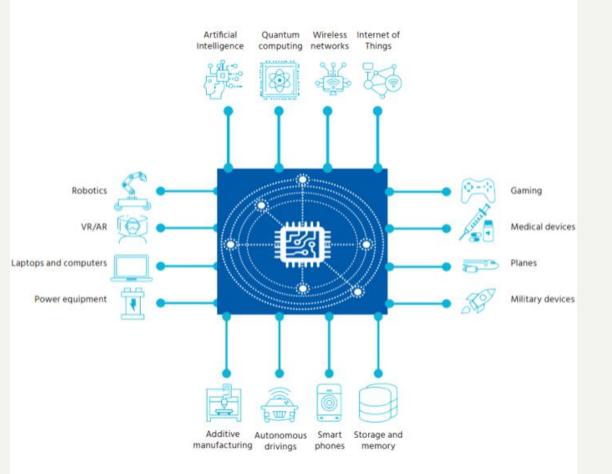

#### Tightly linked to future Electronics growth areas

The increasing amount of semiconductor content in electronic systems is enabling innovation and driving system value growth

Source: VLSI Research, September 2021

#### **Current Market Drivers in Electronics**

- 5G wireless network deployment will see major footprint in cars' connectivity

- Renewables faces governments' focus with the new climate agreements

- The slow adoption of electric vehicles is facing a turnaround

- Businesses using IoT technologies from 13 % in 2014 to 25 % in 2020

- AI/ML applications are increasing needs for HPC

Consumption of semiconductors per person in China: \$16.72 per person in 2010 \$85.22 in 2020 (+5.10X) (IBS)

#### Learning from other industries

#### "In the year 2054, the entire defence budget will purchase just one aircraft."

Calvin Coolidge's Revenge In 2100, aircraft cost projected to \$ be \$3.6Q per ONE QUINTILLION unit...equal to the If the U.S. defense budget grows projected value of ONE QUADRILLION by 2.5% per year... the entire U.S. GNP If nominal gross national product ONE TRILLION In 2054, aircraft cost grows by 5.5% per year.... projected to be \$800B per ONE unit...equal to the BILLION projected value of the ONE entire U.S. defense MILLION budget ONE THOUSAND 2000 2050 2100 2150 1950 YEAR OF INITIAL OPERATIONAL CAPABILITY THEN-YEAR DOLLARS

#### Integrate, then build!

#### Page 6 Unrestricted | © Siemens 2023 | Siemens Digital Industries Software

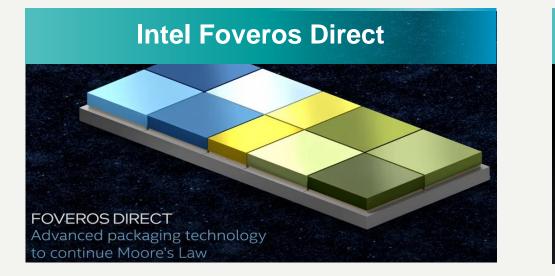

### Getting More out of Moore's Law with High Density Advanced Packaging

# <section-header>

#### **AMD 3D Chiplets**

#### **New Protocols**

#### Universal Chiplet Interconnect Express

Building an open ecosystem of chiplets for on-package innovations

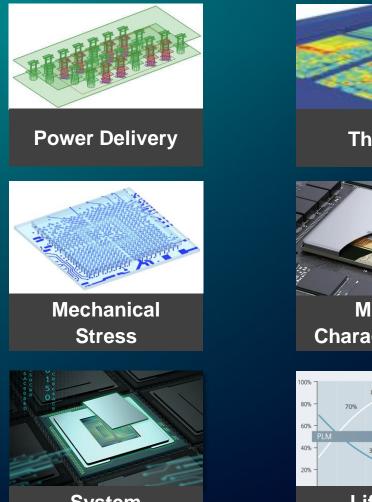

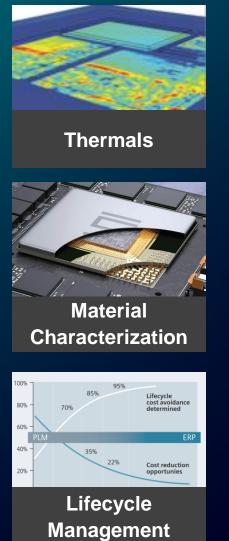

#### **New Challenges Presented by New Frontiers**

System Integration

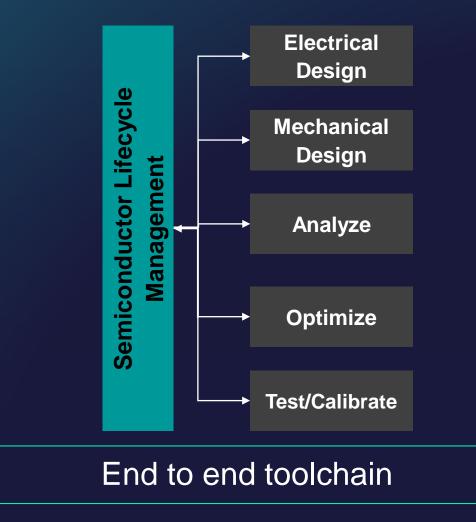

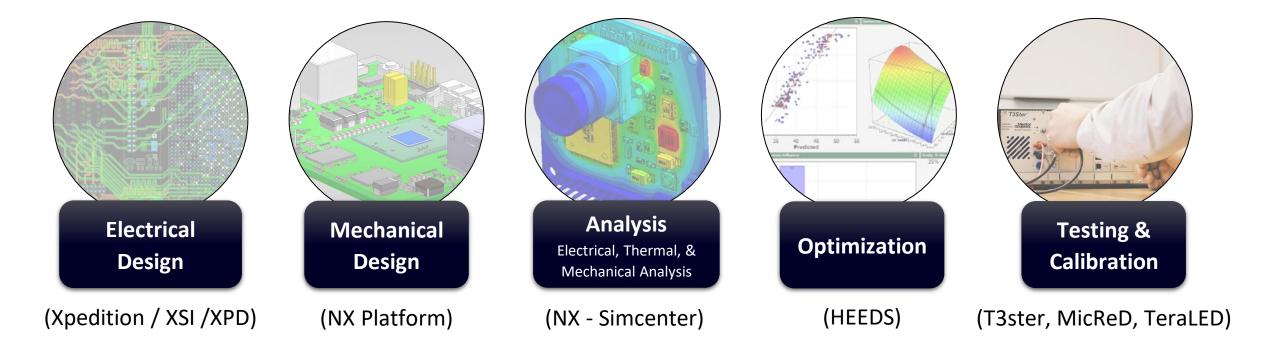

#### **Integrated Advanced Packaging Design Workflow**

## **Thermal Measurements**

**Basics**

Page 10 Unrestricted | © Siemens 2023 | Siemens Digital Industries Software

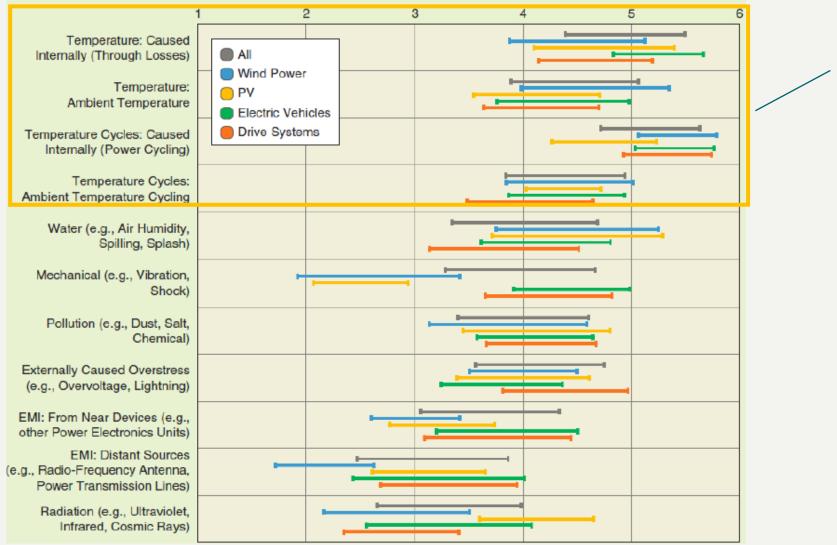

#### **Temperature Factors - Main Threat to Reliable Operation**

Temperature related issues have highest votes

Source: J. Falck, C. Felgemacher, A. Rojko, M. Liserre and P. Zacharias, "Reliability of Power Electronic Systems: An Industry Perspective," in IEEE Industrial Electronics Magazine, vol. 12, no. 2, pp. 24-35, June 2018.

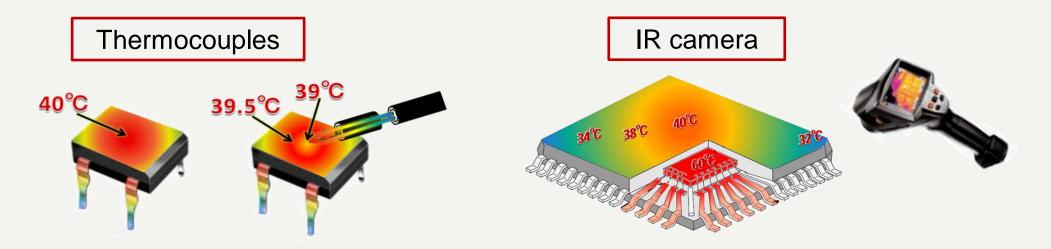

#### **Traditional Measurement Solutions**

SIFMENS

- Simple and generally available methods

- Only surface temperature (Thermocouples, IR camera)

- Effect by thermocouple itself or surface, emissivity and absorptivity

- Require access to the die to measure junction temperatures

#### Page 12 Unrestricted | © Siemens 2023 | Siemens Digital Industries Software

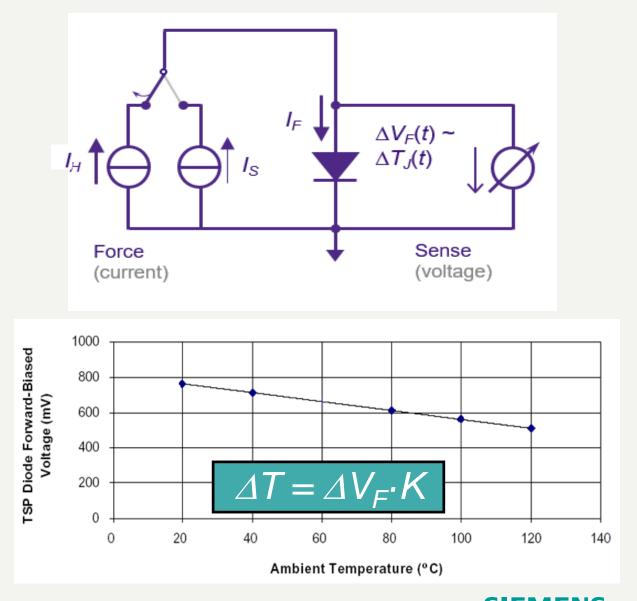

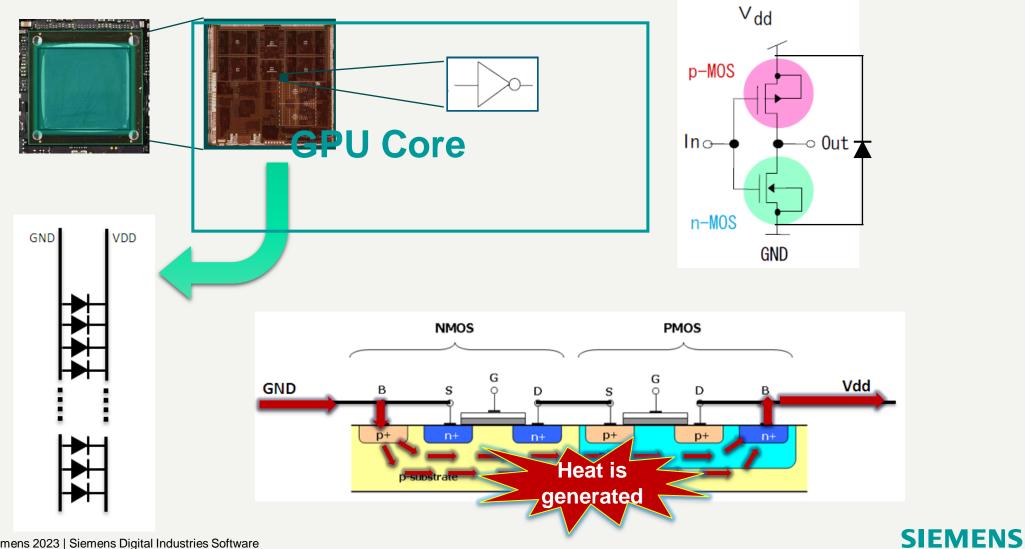

#### **Accurate Junction Temperature Measurement**

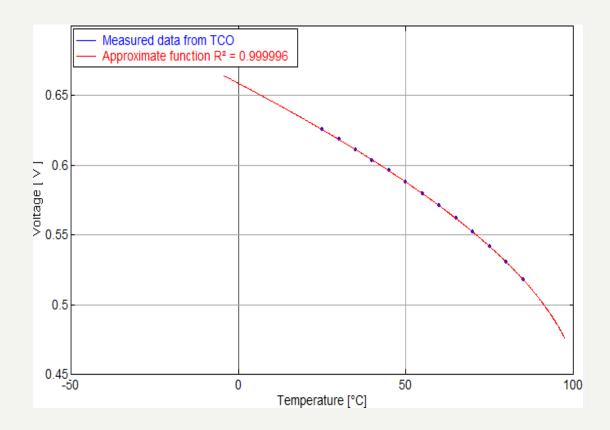

- The forward voltage of a PN junction under forced current condition can be used as a very accurate thermometer

- The change of the forward voltage (TSP temperature sensitive parameter) should be carefully calibrated against the change of the temperature (see JEDEC JESD51-1 and MIL-STD-750D)

- In the calibration process the S<sub>VF</sub> temperature sensitivity of the forward voltage is obtained

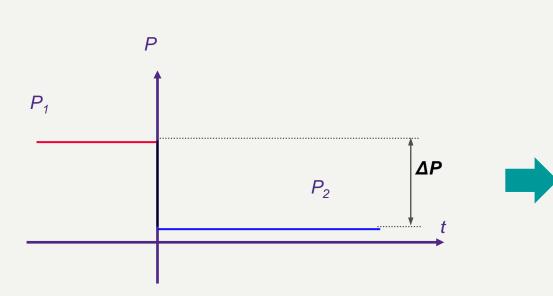

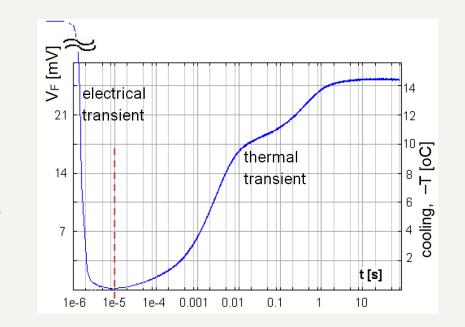

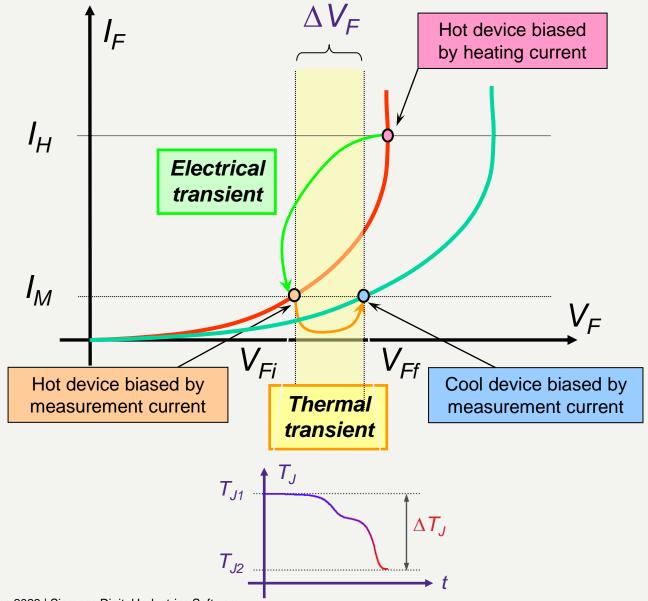

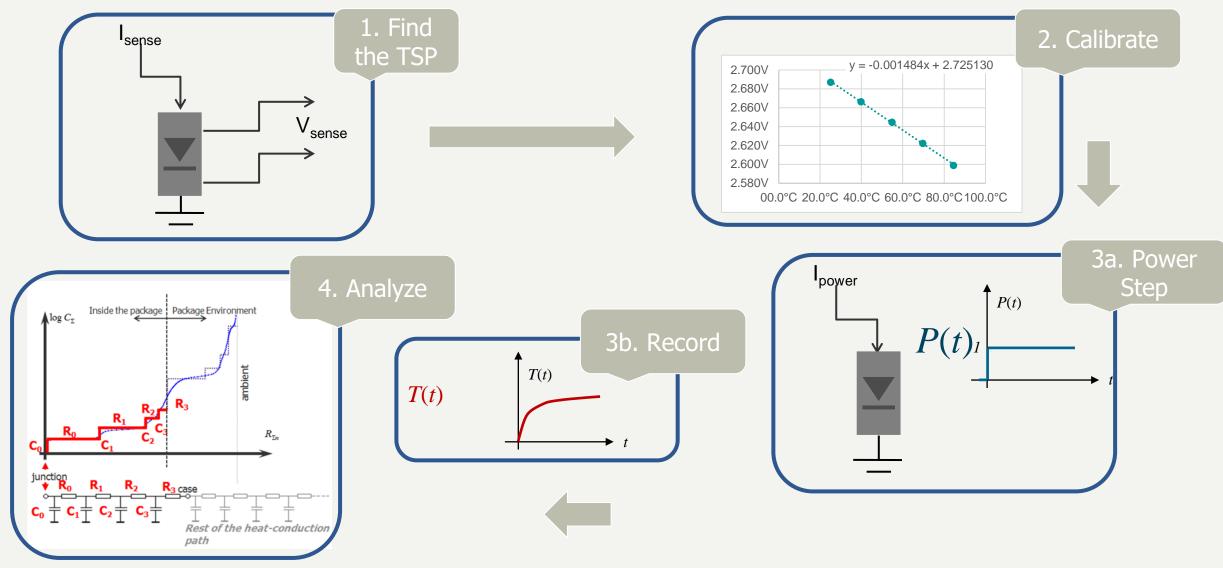

#### How is the Measurement Done?

- Static test method (JEDEC JESD 51-1 standard) Very fast switching between heating and sensing states

- Fast measurement at "junction" to capture time constants

- High temperature resolution: 0.01°C in practice

- 4-wire setup (Kelvin setup) for better power accuracy

#### How is the Measurement Done?

#### What preparations are necessary for a test?

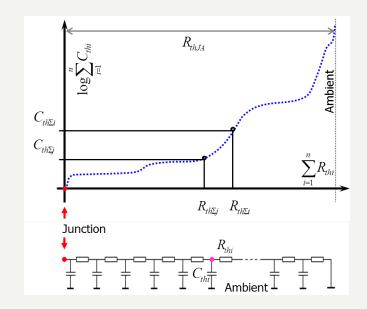

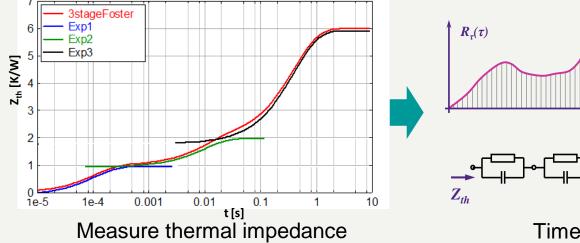

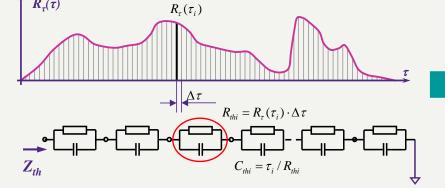

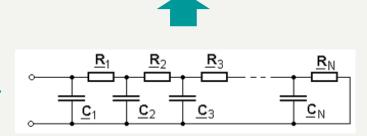

#### **Analyzing the Structure**

Time constant spectrum

Foster-Cauer Transformation

## **Thermal Measurements**

**Test environments**

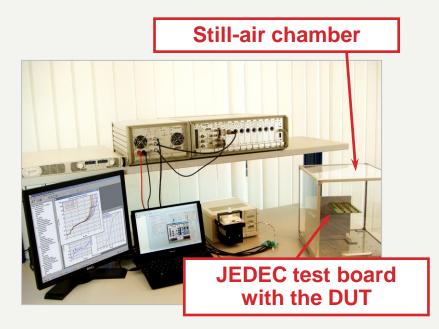

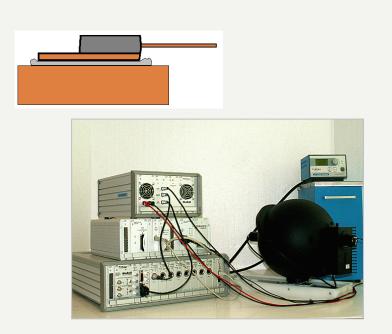

#### **JEDEC** standard test conditions

Besides test equipment, standard test conditions need to be provided test environments

- natural convection

- forced convection

- cold plate

device fixtures / test boards

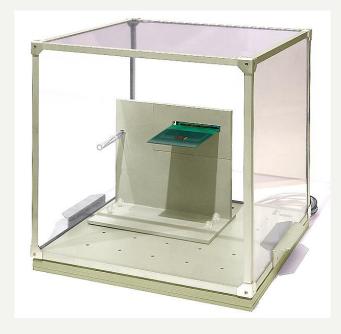

Natural convection: JEDEC JESD51-2A standard

Forced convection: JEDEC JESD51-6 standard

Different test boards: JEDEC JESD51-3, 5, 7, 10, 11

Source of image http://www.utacgroup.com/technology\_contents\_analysis2.html

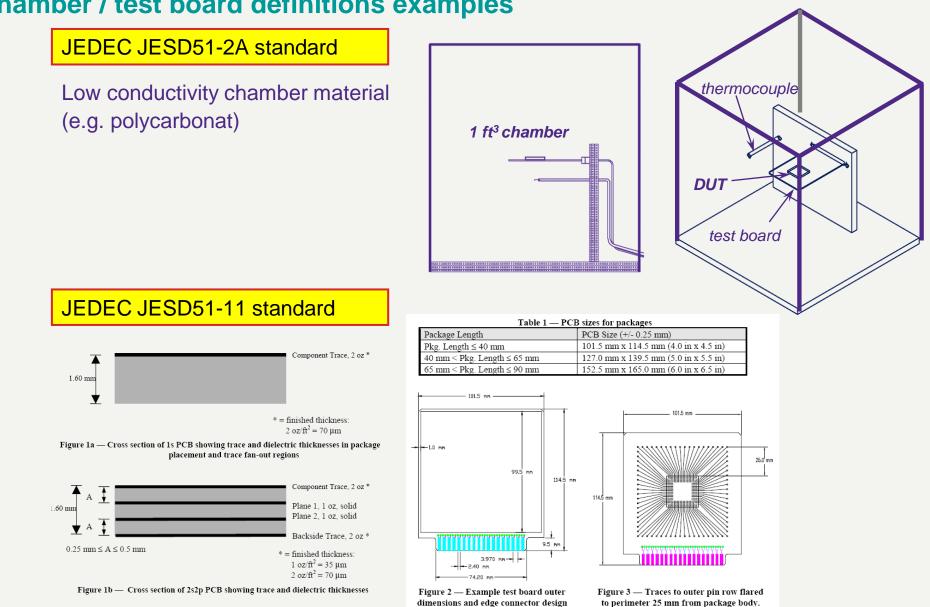

#### **Still-air chamber / test board definitions examples**

#### SIFMENS

#### **JEDEC** standard test conditions

#### Test environments

natural convection: 1 ft<sup>3</sup> still-air chamber: **JESD51-2A** (2008) forced convection: wind tunnel JESD51-6 (1999)

Test boards

copper coverage / number of layers

high / low conductivity, 1s / 2s

different designs mathching different package styles

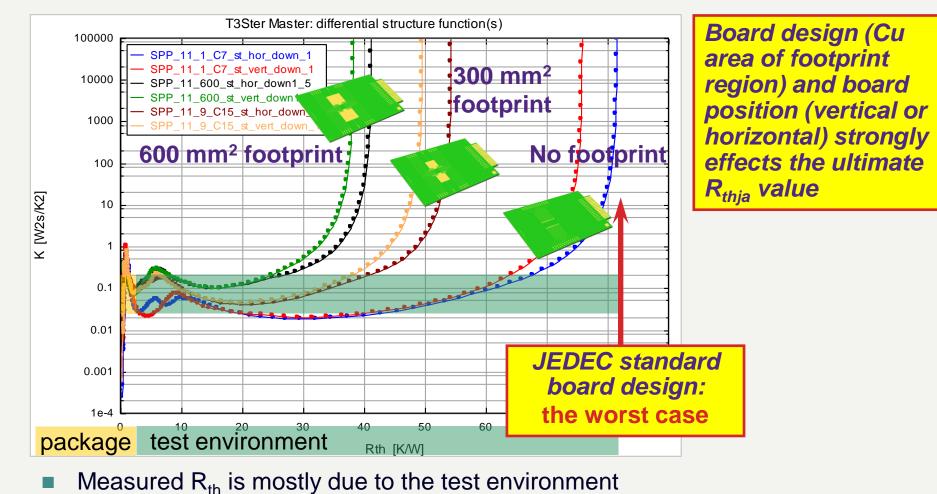

design / orientation counts a lot, as shown by structure functions

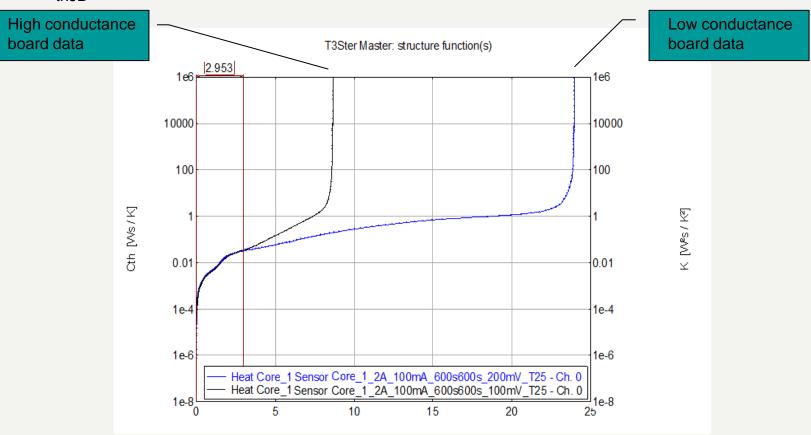

#### Effect of test board design / orientation

Tests performed in a JEDEC standard still-air chamber Measured transients converted to structure functions

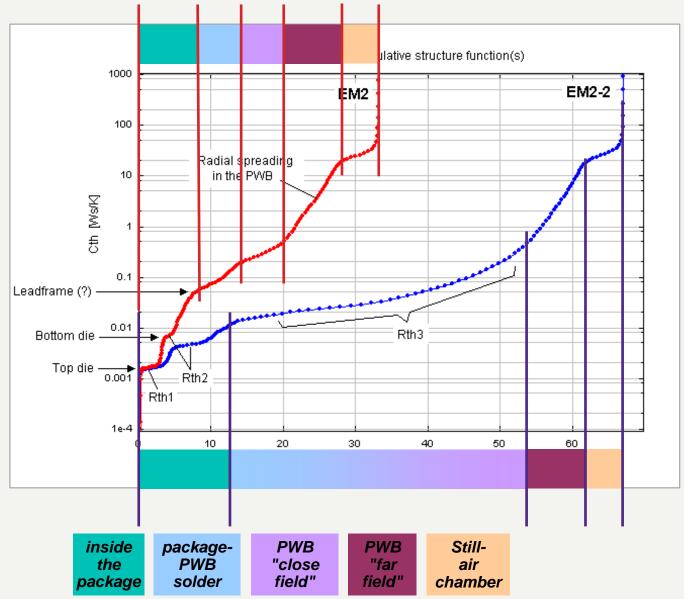

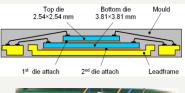

#### **Example: Two live chips stacked in a 44L LLP package**

Stacked die package tested in JEDEC standard test environment

Transient extension of the JESD51-1 static test method was used, followed by structure function analysis

#### **Results in terms of structure functions**

Majority of the  $R_{thja}$  is caused by the JEDEC standard test environment.

Page 24

Unrestricted | © Siemens 2023 | Siemens Digital Industries Software

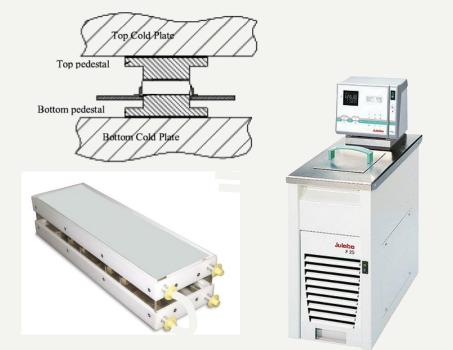

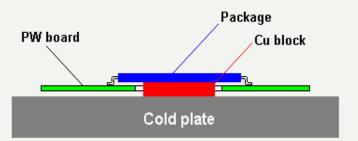

#### **Cold plate as a test environment**

Single cold plate setups for R<sub>thJC</sub> measurements also, test based models of power packages (transient extended JEDEC 2R models)

Quicker test, shorter heat-flow path, results characteristic to the package

Dual cold plate setups for DELPHI boundary conditions

- validation of detailed models of test set of boundary conditions

- DCP1, DCP2, DCP3, DCP4 setups

## **Thermal Measurements**

Different ways to get the TSP

Page 26 Unrestricted | © Siemens 2023 | Siemens Digital Industries Software

#### The 'body diode' method

#### **Body diode method example**

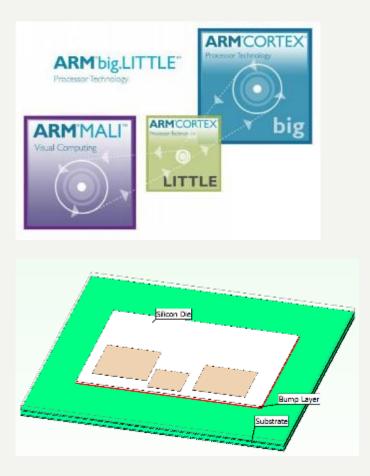

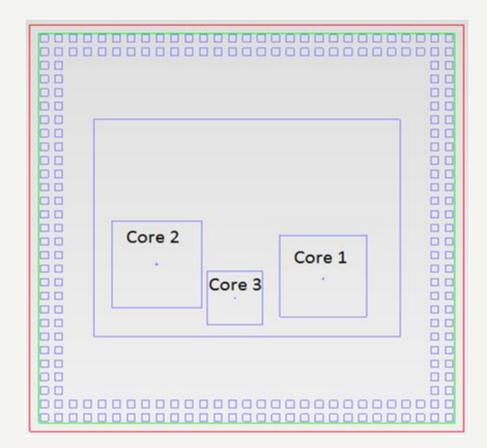

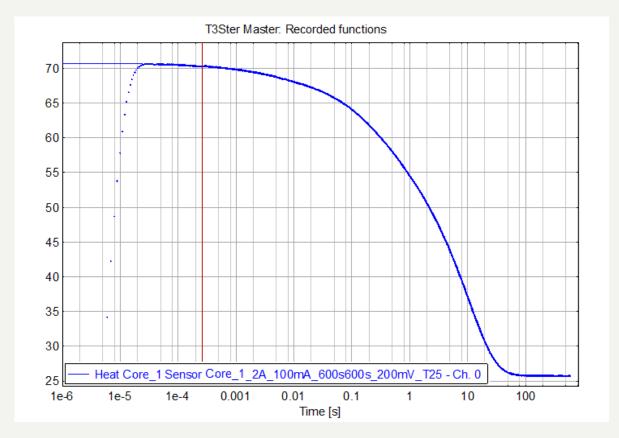

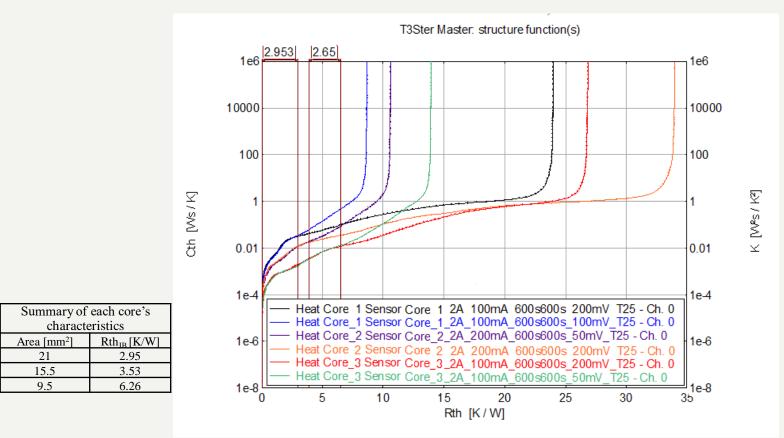

The SoC sample has three cores, 'Core 1 to 3' embedded onto one silicon die. Core 2 also contains an embedded capacitance which requires us to select to corresponding sensor current carefully.

#### **Selection of sensor current**

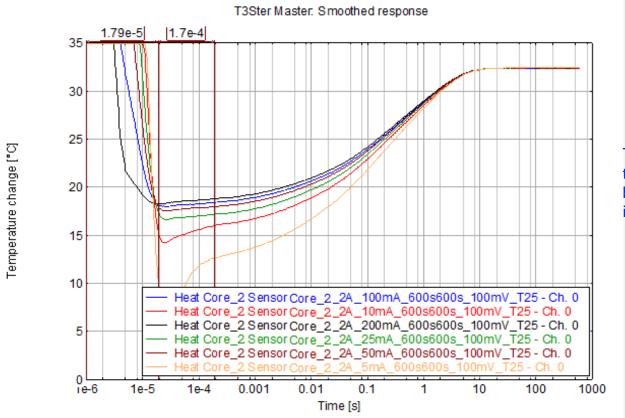

Thermal transient measurement were performed on Core 2 with different sensor current values, starting from 5mA and going up to 200mA. The heating current was 2A in each case.

The sensor current is 200mA, the electric transient ends below 20 microseconds, which is a significant gain.

#### **K-factor calibration results**

Page 30

K-factor on Core 2 is non-linear due to the capacitance, however it is highly repeatable. 3rd order polynomial fit was applied on the measured point instead of a linear approximation.

#### **Thermal transient data**

After successful calibration of each core, thermal transient tests were performed, two tests on each core.

#### **Measurement results**

The structure functions corresponding to the device mounted on high conductance board and low conductance board overlap until the R<sub>thJB</sub> value.

#### **Measurement results**

Depending on the heat source area, both the initial thermal capacitance resolved by the structure functions and the calculated Rth<sub>JB</sub> values will be different.

SIFMENS

Core 1

Core 2

Core 3

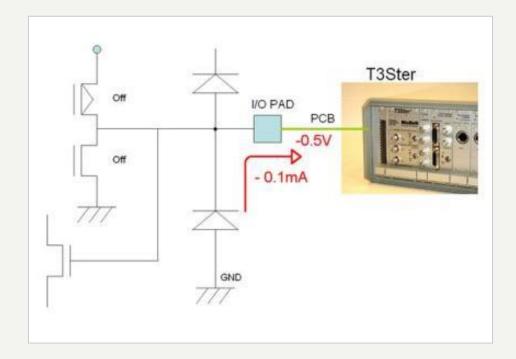

#### **Alternate option – Use of ESD protection diode**

Measuring one of the ESD protection diodes at a non-used I/O pad

#### Advantages:

• Enables real time measurements while the system is operating

Disadvantages:

- Point like sensor, typically on the I/O ring

- Heated region is different

- Requires additional means to measure power

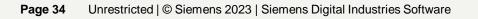

#### **Using TTV-s**

Resistive heater – diode like sensor

The distance between the heating resistor and the sensor diode must be small otherwise a transfer impedance is measured.

Constant  $P_D$  must be assured – if the resistance depends on temperature, cooling curve must be recorded.

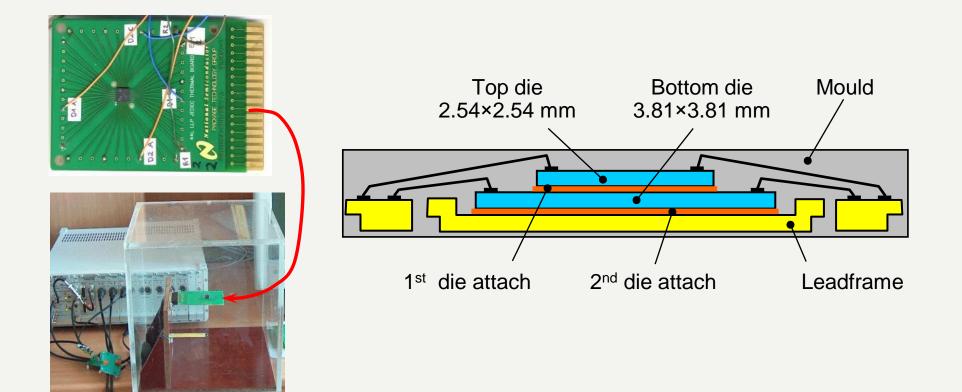

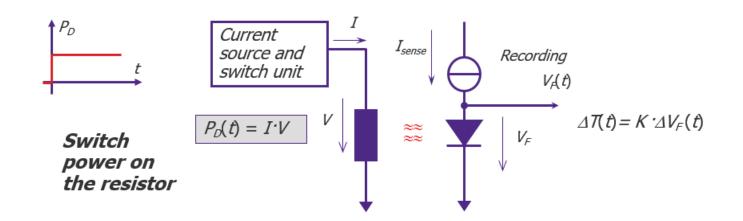

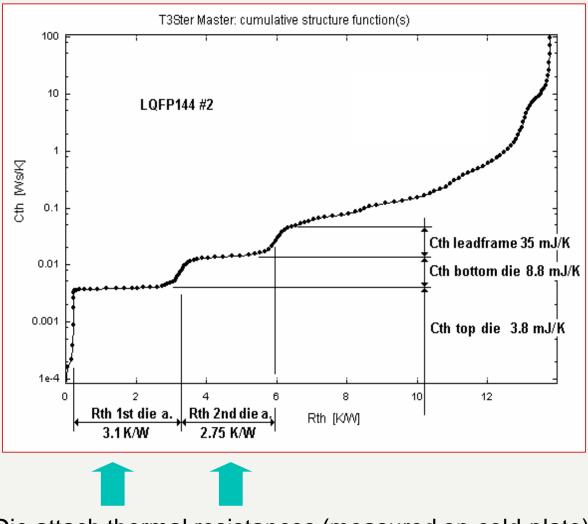

#### **Stacked Test Dies in 144LQFP**

#### Set measurement parameters

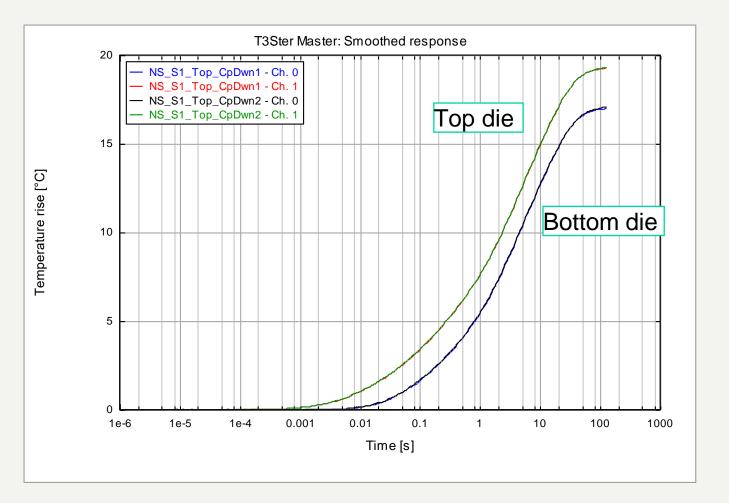

#### **Thermal Transient Test data**

Repeated transients, top die powered, temperature at both junctions captured, fitted at cold point

#### **Structure function information**

Die attach thermal resistances (measured on cold-plate)

## Links to simulation

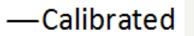

#### **Model Calibration**

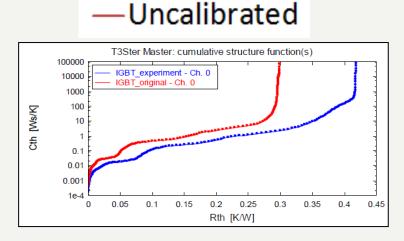

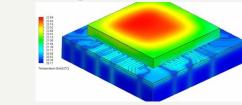

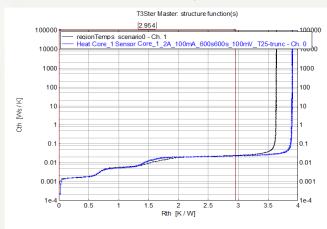

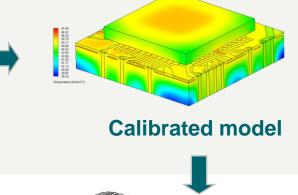

To ensure model accuracy a simulation based Structure Function <u>must</u> match the test based Structure Function across all package elements.

We don't rely on thermocouple measurements

Only then are we ensured that each object in the package is modelled correctly.

Only then are we ensured that the 3D temperature field is accurate

**Only then** are we ensured the simulaton model includes all package time constants and will respond correctly for all driving power profiles.

#### Calibrating simulation models to test data

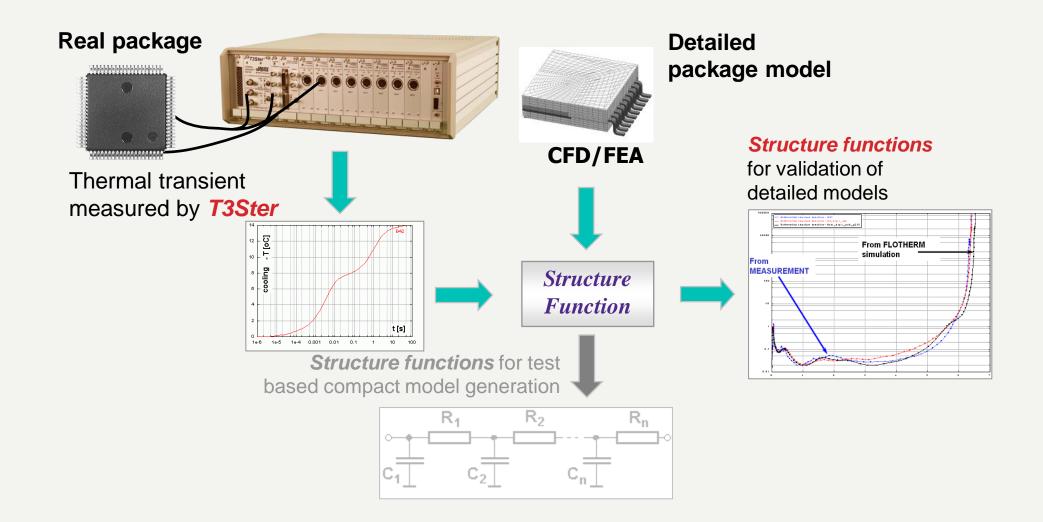

#### **FANTASTIC Method for Reduced Order Models**

L. Codecasa, V. d'Alessandro, A. Magnani, N. Rinaldi and P. J. Zampardi, "<u>Fa</u>st <u>N</u>ovel <u>Thermal Analysis Simulation Tool for Integrated Circuits (FANTASTIC)," 20th</u> International Workshop on Thermal Investigations of ICs and Systems, London, 2014

#### **Ideal Compact Thermal Model:**

Boundary Condition IndependentHigh Accuracy – Known AccuracySupports Multiple Heat SourcesTransient SupportInternal Geometry cannot be reverse engineeredSolves orders of magnitude faster than detailed modelCan be created quickly and reliably

#### **FANTASTIC Accuracy**

- A 'FANTASTIC' Reduced Order Model is accurate for:

- Any set of Boundary Conditions

- Any number of heat sources

- Any driving frequencies, and at all transient time scales.

Unlike any other ROM method, the accuracy is an input!

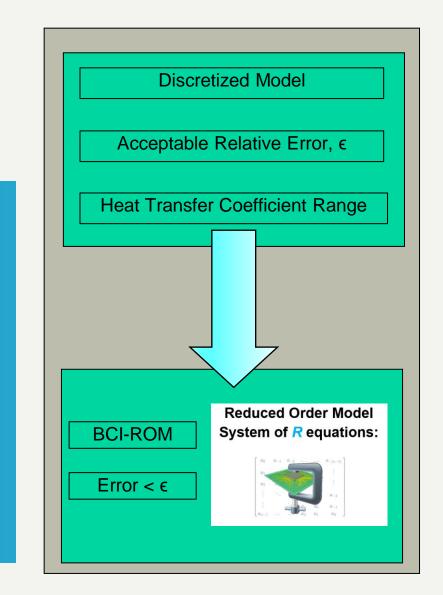

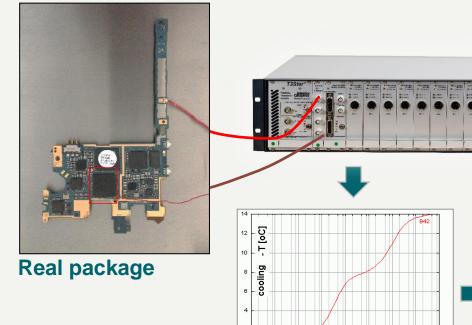

#### **Calibration and BCI ROM workflow**

#### Package model from Vendor

Match structure functions during calibration

System level model with die power map

t [s]

100

1e-6 1e-5 1e-4 0.001 0.01 0.1 1 10

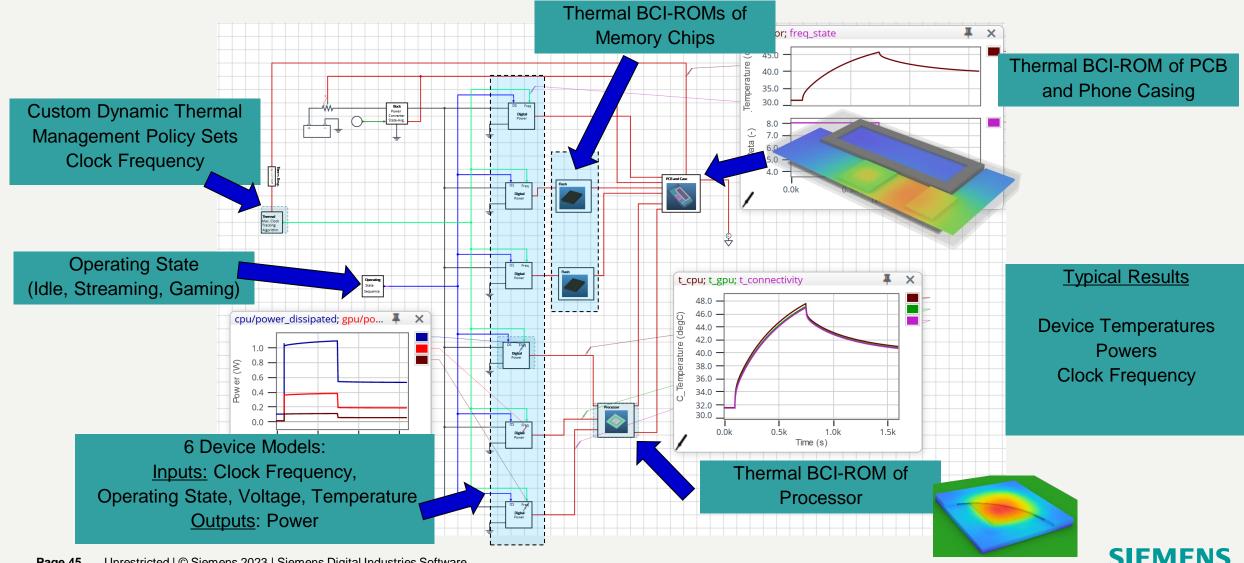

#### **Using BCI-ROMs Mobile Phone Example**

Page 45 Unrestricted | © Siemens 2023 | Siemens Digital Industries Software

#### **Summary**

- Accurate thermal measurement of complex semiconductor packages is possible

- There are multiple choices to select TSP, powering, test environment

- The test data can be transformed to behavioral or structural thermal models

- The test data can be used to supply calibration input to cutting-edge simulations

## Thank you! Questions?

Published by Siemens DISW Andras Vass-Varnai Portfolio Development Executive E-mail andras.vass-varnai@siemens.com