## January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

Fraunhofer IIS/EAS Dresden

## Outline

- Introduction

- Packaging market share

- Roadmap

- Technology trends

- High-End packaging

- Wafer-Level Packaging

- SiP Packaging

- Hybrid Bonding

- Chiplet Packaging

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

## Introduction

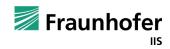

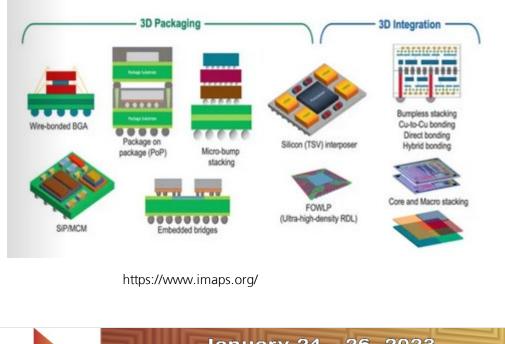

- Wide range of potential packaging technologies available

- Many specific for certain domains

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

## **Packaging market share**

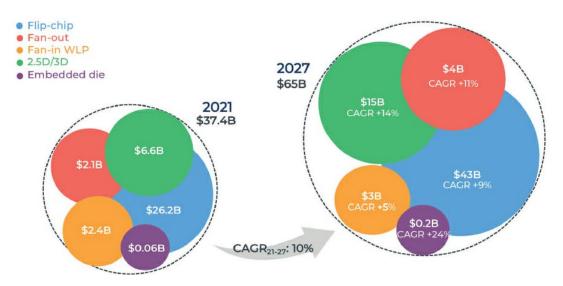

#### 2021-2027 advanced packaging revenue forecast

(Source: Status of the Advanced Packaging Industry 2022, Yole Intelligence, July 2022)

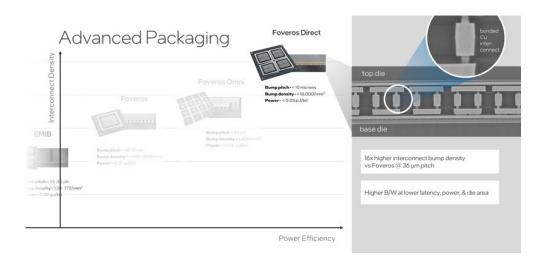

#### Advanced Packaging

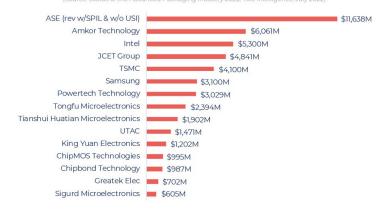

- Big market share in past and currently by OSATs like ASE and Amkor

- IDMs and Foundries like Intel and TSMC are gaining market share

- Largest investments are not from OSAT side with potentially disrupting the market

Estimated 2022 packaging CapEx split (top players)

- Grow expected at around 10% per year

© Yole Développement, 2022

2021 top 15 players involved in advanced packaging - Financial overview

# CHIPPET

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

\*Intel 32%

Tongfu

3%

PTI 4%

> JCET 4%

> > Amkor

6%

\$15B

\*Samsung

11%

#### Annual Update on Packaging

ASE

13%

\*TSMC

27%

## **Packaging market share**

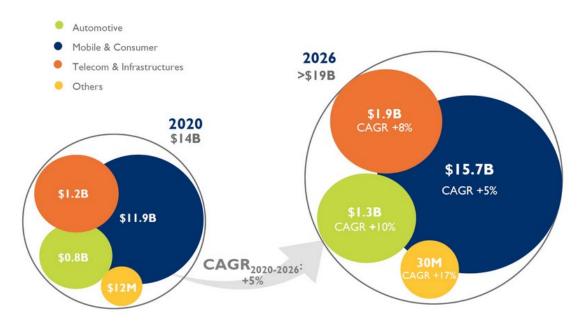

#### System in package (SiP)

- Largest amount on market share in packaging is in respect to SiP

- Dominated by the mobile market, which will be the largest market for the upcoming years

- Grow is slightly smaller than packaging market in general

- Saturated market with spans across IDM, Foundries and OSATs

#### 2020-2026 System-in-Package market forecasts breakdown by market segment

(Source: System-in-Package Technology and Market Trends 2021, Yole Développement, July 2021)

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

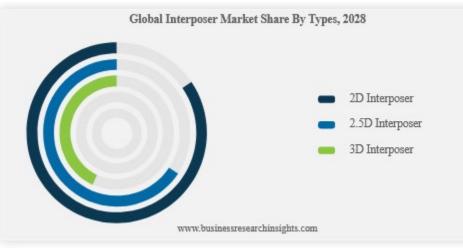

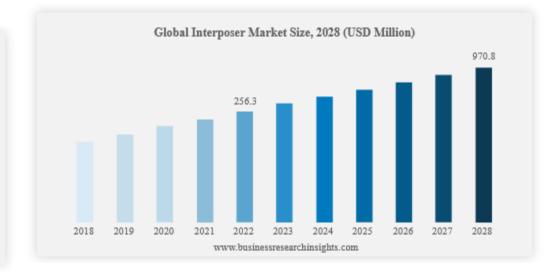

## **Packaging market share**

#### Interposer

- Currently small market share in packaging with ~250M\$

- But estimated high growth rate of around 20%

- North America dominated due to higher costumer demands

- "classical" 2D interposer have the largest market share

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

## **Packaging Roadmap**

#### Pitch and spacing view

- Still ongoing trend to smaller feature sizes

- But only limited reduction expected in bump and ball pitch

- Largest achievements in pitch reduction are expected in Hybrid bonding

- with wafer2wafer already mature for very fine pitches

- And major advances are expected in die2wafer and also die2die bonding

#### Advanced packaging roadmap: I/O pitch and RDL L/S

(Source: Status of the Advanced Packaging Industry 2022, Yole Intelligence, July 2022)

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

## **Packaging Roadmap**

#### SiP

Still ongoing trend to smaller feature sizes

#### 2017-2025 SiP technology roadmap - key parameters

(Source: System-in-Package Technology and Market Trends 2021, Yole Développement, July 2021)

|                         | Metrics                  | <2017             | 2019            | 2022        | 2025       | SiPAdvancement  |

|-------------------------|--------------------------|-------------------|-----------------|-------------|------------|-----------------|

|                         | Substrate RDL L/S        | 30/30 to 10/10 µm | 10/10 to 5/5 μm |             | 8/8 to 5/5 | FC BGA SiP      |

| Flip Chip<br>Substrate) | Substrate I/O Pitch      |                   | 1200 to 350 µm  |             | 300 µm     |                 |

| Chip                    | Substrate I/O Ball       | 500 - 3000        |                 | >> 3000     |            |                 |

| Flip Chip<br>Substra    | Max Package Size         | > 65x65 mm        |                 | >> 80x80 mm |            | Double-Sided    |

| <u> </u>                | Max no. of Dies/Passives | < 15              | < 35            | >> 35       |            | FC SiP          |

|                         | Max level of RDLs        | 10 - 16>          | RDL             | >>          | 10x RDL    | C.C. Market and |

|                         | Substrate RDL L/S        | 15/15 to 8/8 µm   | 5/5 ! m to      | o 2/2 µm    | < 1/1 µm   | FO on Substrate |

|                         | Substrate I/O Pitch      | 400 µm            | 350 µm          | 200 μm      |            |                 |

| Fan-Out                 | Substrate I/O Ball       | < 300             | 600 -1300       | >           | >> 1500    |                 |

| an                      | Max Package Size         | < 5x5 mm          | < 25x25 mm      |             | < 30x30 mm | HD FO SiP PoP   |

|                         | Max no. of Dies/Passives | ≤ 2               | ≤ 4             |             | ≤ 6        |                 |

|                         | Max level of RDLs        | 3x - 4            | « RDL           | >           | 4x RDL     | <b>5</b>        |

|                         | Substrate RDL L/S        | > 25/25 µm        | > 20/20 µm      |             | > 15/15 µm | Embedded        |

| Die                     | Die I/O Pitch            | <b>250-80 μm</b>  |                 | 50 µm       |            | Interconnects   |

| ded                     | Die I/O Numbers          | 40-100            | 100             | -150        | 150-200    |                 |

| ede                     | Max Package Size         | <15x15 mm         |                 | < 25x25 mm  |            | Embedded        |

| Embedded                | Max no. of Dies/Passives | ≤ 2               | 5               | 3           | ≤ 4        | Multi-Dies      |

|                         | Max level of RDLs        | 2x - 4x RDL       |                 | 4x – 6x RDL |            | 00000000        |

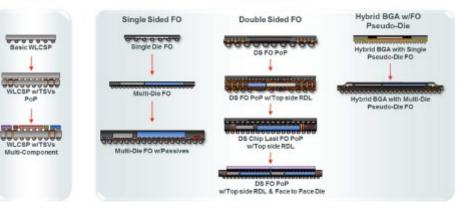

## **Packaging Roadmap**

#### Wafer Level Packaging

- In general two different types

- Fan-in

- Fan-Out

Mobile (90% market)

#### . Market Drivers & Capabilities

- Small footprint

- Better electrical performance .

- Lower cost package:

- Thinner package Lower thermal resistance

Fan In

WLP

Fan Out

WLP

**Enabling Technologies**

- Wafer Processing

- Bumping

٠

Thin Film RDL

#### WLCSP

PoP

- Mobile (90% market) (LD & MD)

- Networking (HD)

- **Market Drivers & Capabilities**

- . Small footprint

- Better electrical performance .

- Lower cost package: .

- Thinner package ٠

- Lower thermal resistance

- Larger Package Size

- Improved Reliability performance .

- PoP Package capability -

- . SiP Package capability

#### Enabling Technologies

- Wafer Processing . Wafer Molding .

- . Bumping Thin Film RDL

.

.

Low Temp cure RDL Polymer Panel Processing

#### Fan Out

http://eps.ieee.org/hir

CHIR

January 24 - 26, 2023 **DoubleTree by Hilton San Jose** ChipletSummit.com

#### Annual Update on Packaging

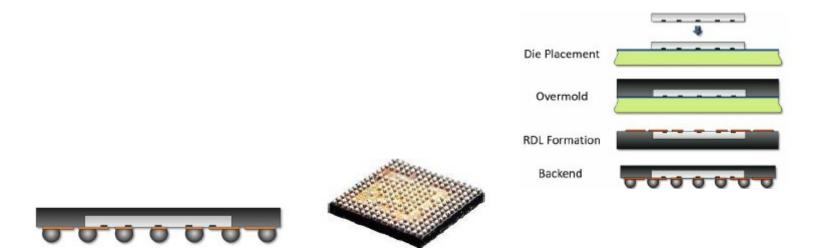

#### eWLB

- One variant of Fan-Out package

- Mostly for lateral communication

- Used by many packaging suppliers

- E.g. ASE FOCoS

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

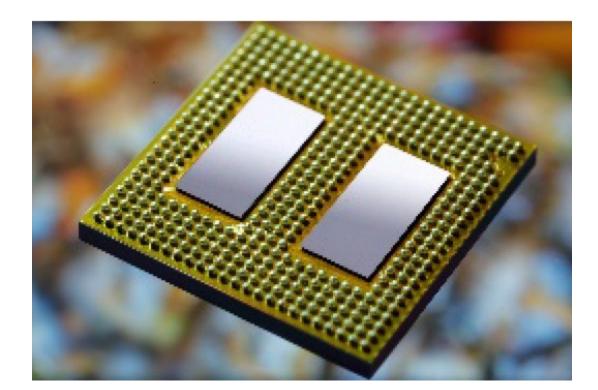

#### Face2Face IC assembly

- Assembly of ICs to another IC to separate functions to different Processes (like compute and memory, or compute and logic

- Comprehensive design of system

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

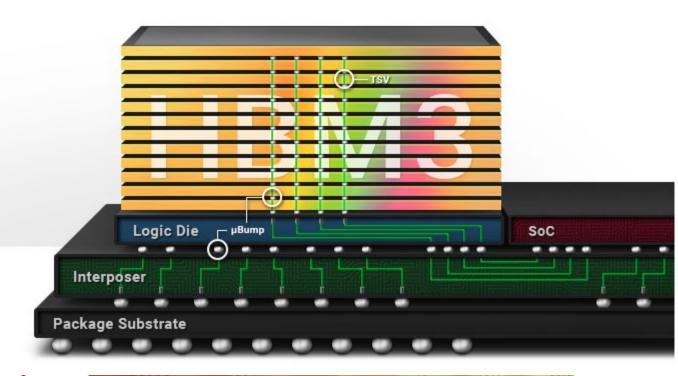

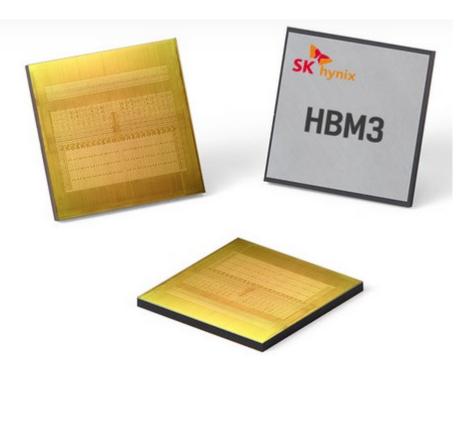

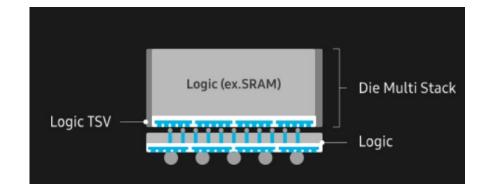

#### **3D-Stacking**

E.g. HBM3 with up to 12 stacked dies from SK hynix

CHIPLET

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

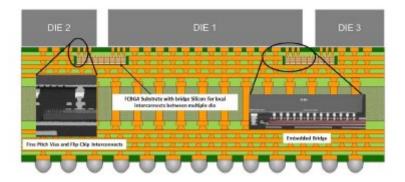

#### Intel EMIB

Rigid bridge based on silicon with fine line and space for high density interconnect

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

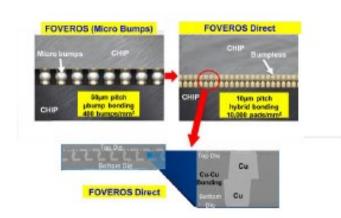

#### **Intel Foveros**

First shipping in 2020 with "Lakefield" processor generation

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

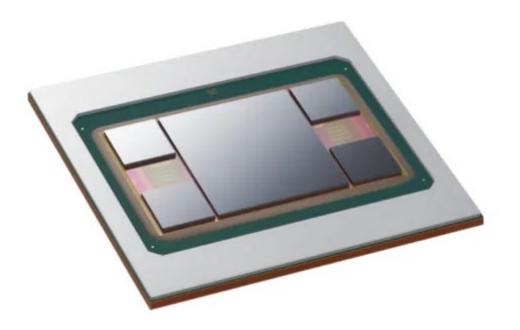

#### Samsung Foundry Cube Technologies

- I-Cube

- 2.5D Si Interposer

- Either wafer-level or substrate level

- MiM and integrated stacked capacitor (ICP) embedded in interposer

- Sizes up to 1600mm<sup>2</sup> qualified

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging © Fraunhofer IIS/EAS

Fraunhofer

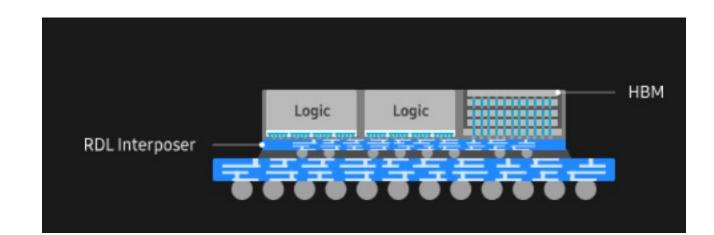

#### Samsung Foundry Cube Technologies

- R-Cube

- Using RDL interposer

- No TSVs

- More flexibility

- But not such fine line/space compared to silicon interposer

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

#### Samsung Foundry Cube Technologies

- X-Cube

- Higher density due to 3D stacking

- Higher bandwidth and lower latency

- Less degree of freedom

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

#### Samsung Foundry Cube Technologies

- H-Cube

- Also called 5.5D system because 2.5D system stacked as 3d

- Cost effective

- Good scaling

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

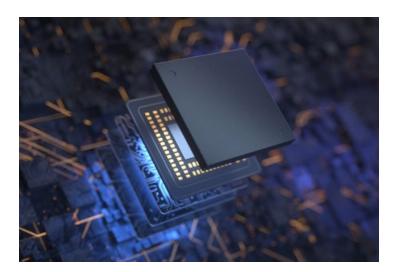

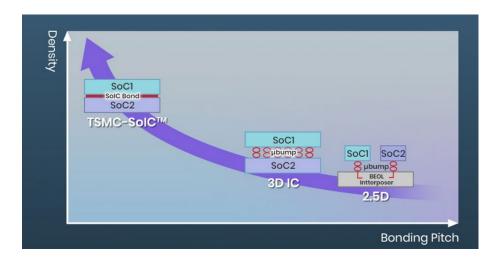

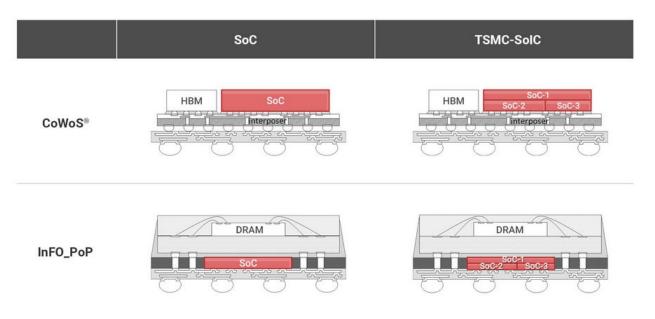

#### **TSMC SolC**

- 3D inter-chip stacking technology

- Integration of chiplets portioned from SoC

- Meet increasing compute, bandwidth and latency requirements

CHIPLET

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

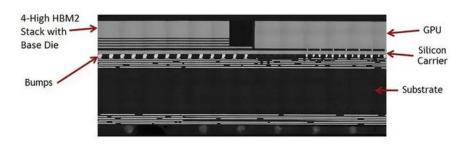

#### **TSMC CoWoS**

- As 2.5D package using RDL-based interposer CoWoS-R

- As 2.5D package using silicon-based interposer CoWoS-S

CHIPLET

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

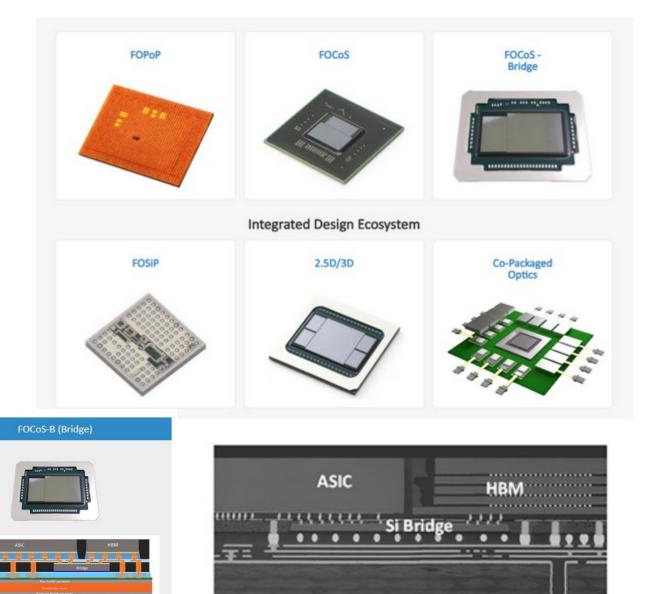

#### ASE

- FOCoS (Chip on Silicon)

- Lower cost (vs. 2.5D)

- Thinner package

- Good electrical performance (shorter D2D connect)

- High I/O counts (> 1000)

FOCoS-CF (Chip First)

0000000000

Time to market with existing Fan-Out/Flip

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

FOCoS-CL (Chip Last)

Annual Update on Packaging

#

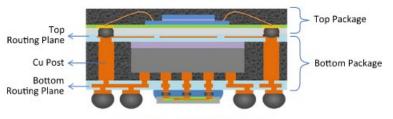

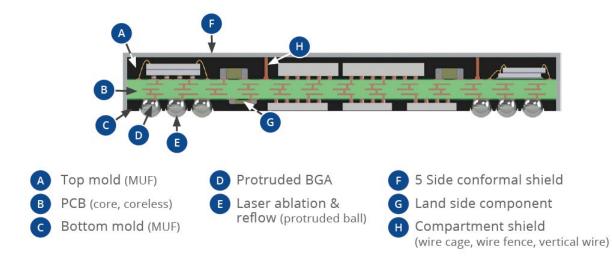

### ASE

- FOPoP (Package on Package)

- 3D integration of Memory device and Logic device

- System size reduction and Board space savings

- Memory architecture flexibility

- Shorten signal routes

- Compatible with current assembly technologies

```

Partial Cross-section view of FOPoP

```

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

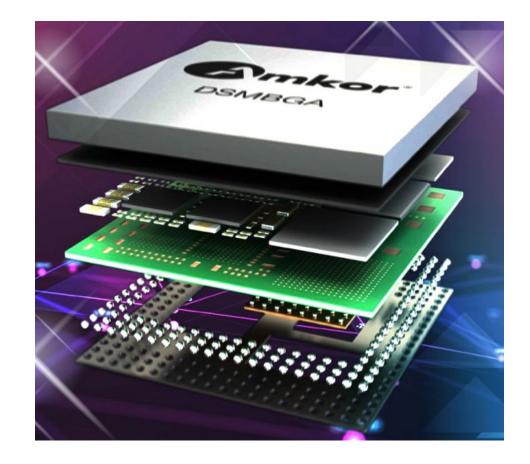

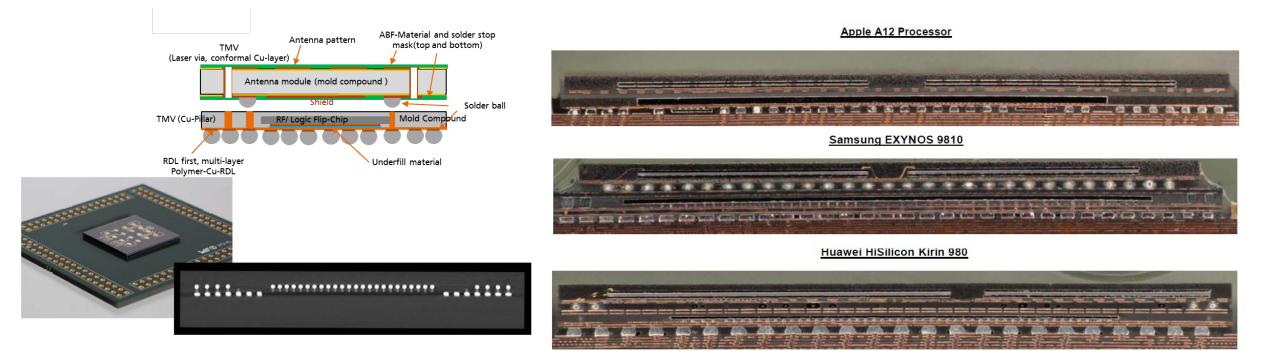

#### Amkor

#### DSMBGA

- Double-Sided Molded Ball Grid Array

- Especially for RF front-end modules

Annual Update on Packaging

Fraunhofer

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

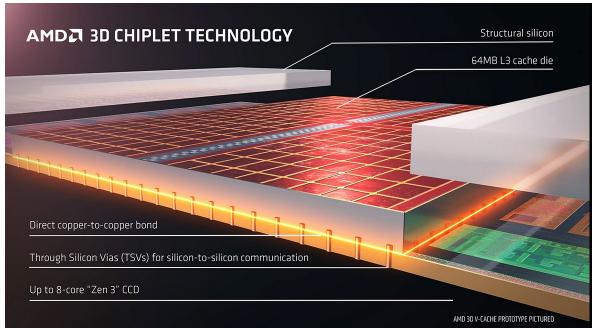

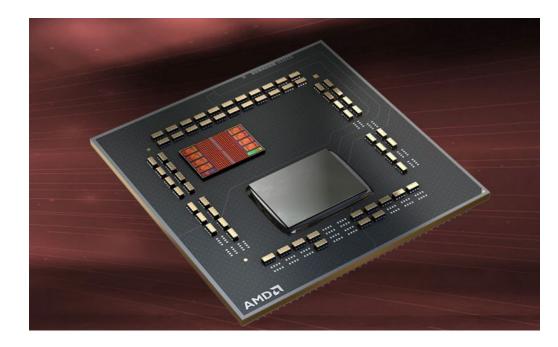

#### AMD 3D V-Cache

- TSMC 7nm CPU combined with SRAM cache using chiplets and hybrid bonding

- Minimum pitch at 9um

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

© Fraunhofer IIS/EAS

Fraunhofer

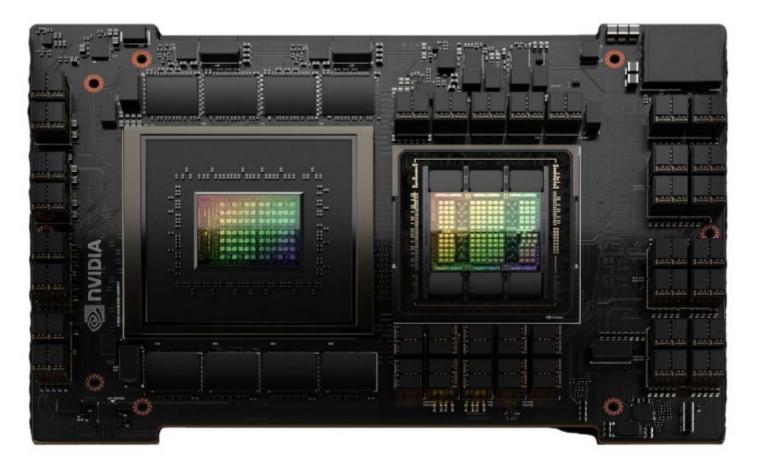

#### Nvidia Grace Hopper

- 72 CPUs connected to 512GByte LPDDR5 memory

- 128 GPUs connected to 96GGbyte HBM

- Packaging view

- CPUs and GPUs on separate interposers

January 24 - 26, 2023

ChipletSummit.com

**DoubleTree by Hilton San Jose**

Package substrate for complete system

Annual Update on Packaging

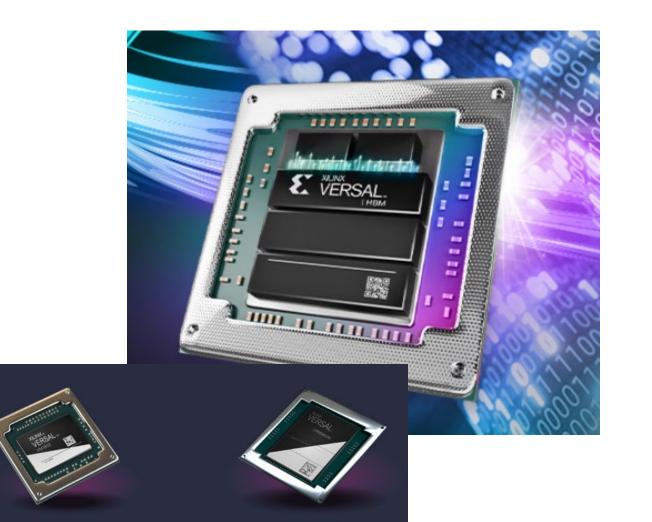

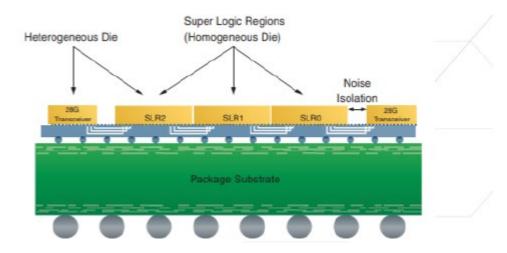

#### Xilinx VERSAL

- Adaptive Compute Acceleration Plattform (ACAP)

- With leading edge VERSAT HBM system

- Based on stacked silicon integration

January 24 - 26, 2023 **DoubleTree by Hilton San Jose** ChipletSummit.com

Annual Update on Packaging

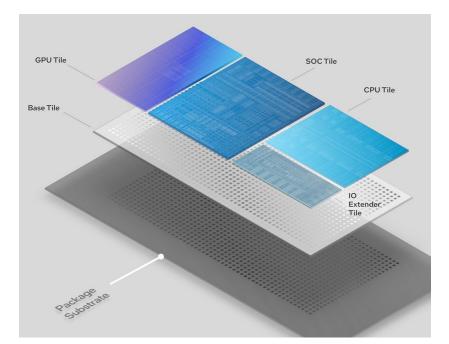

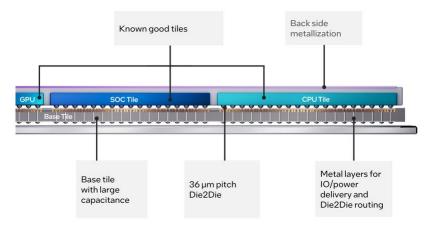

#### **Intel Meteor Lake**

Using Foveros Direct (Cu-Cu hybrid Bond)

## CHIPMET

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

#### Annual Update on Packaging

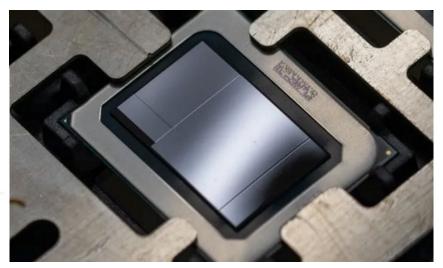

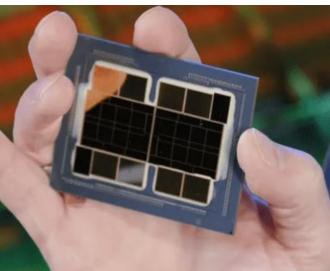

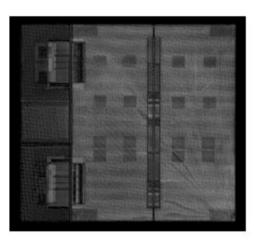

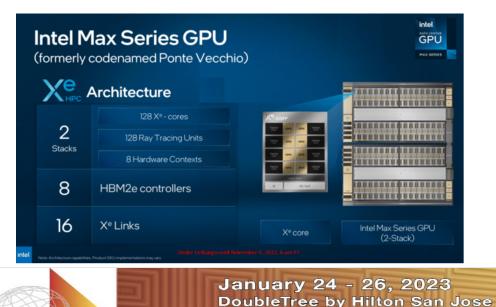

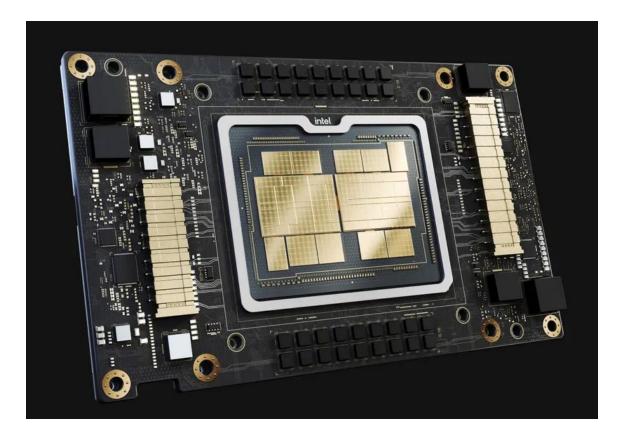

#### **Intel Ponte Vecchio**

- 47 chiplets with a sum of 100 billion transistors

- Combined 2.5D and 3D technology

- 3100mm<sup>2</sup> of silicon

- Using Co-EMIB

- Purpose: for super computer in three variants (with 300, 450 and even 600 Watt)

ChipletSummit.com

Annual Update on Packaging

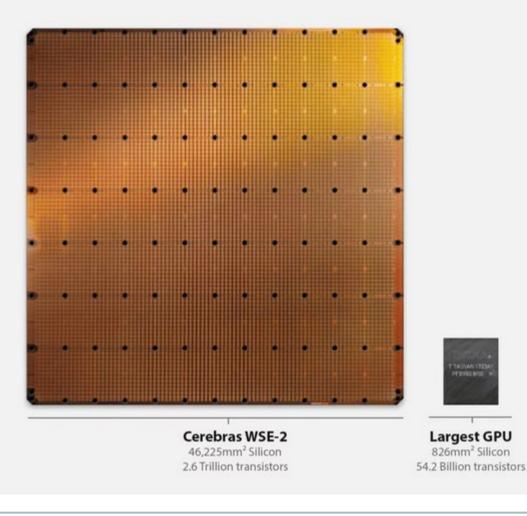

#### Large Scale ICs

- Example from Cerebras

- Almost wafer-scale

- 850,000 cores

- Bandwidth 220 Pb/s

|                  | WSE-2            | A100              | Cerebras Advantage |

|------------------|------------------|-------------------|--------------------|

| Chip Size        | 46,225 mm2       | 826 mm2           | 56 X               |

| Cores            | 850,000          | 6912 + 432        | 123X               |

| On-chip memory   | 40 Gigabytes     | 40 Megabytes      | 1,000 X            |

| Memory bandwidth | 20 Petabytes/sec | 1.6 Terabytes/sec | 12,733 X           |

| Fabric bandwidth | 220 Petabits/sec | 4.8 Terabits/sec  | 45,833 X           |

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

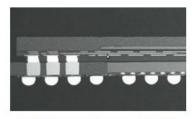

#### Package-on-Package

• For instance for RF applications

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

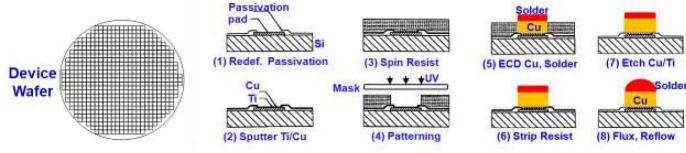

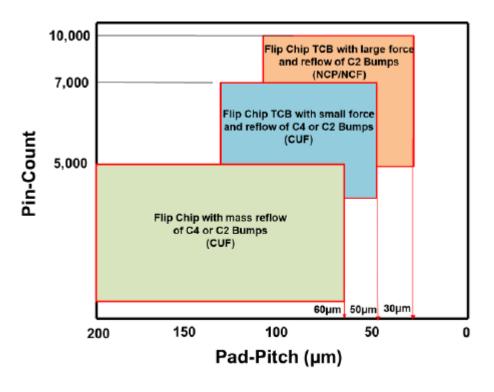

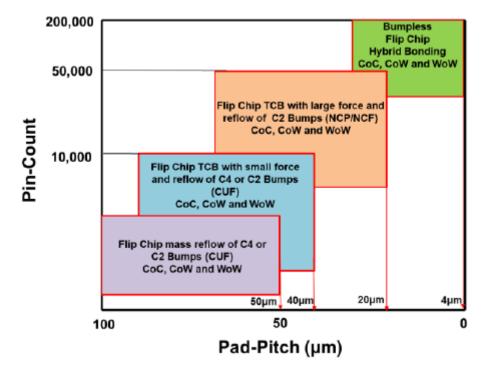

#### Bumping

- Almost all advanced packages are related to bumped devices or hybrid bonding

- Different options, like Au or Ni bumps, Cu studs, solder bumps

- C4 (controlled collapse chip connection) most common one today

- C2 (chip connection), like copper pillars for very high-density and fine pitch

https://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=9684894

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

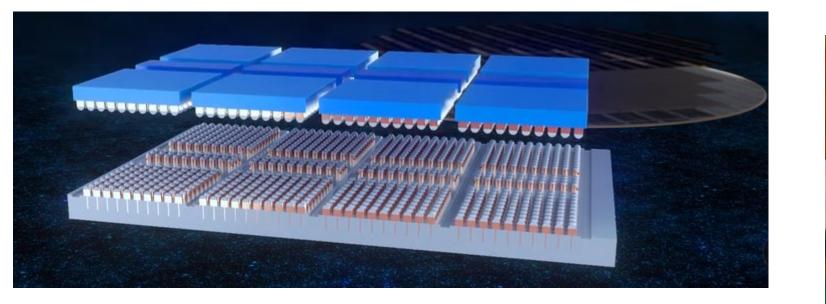

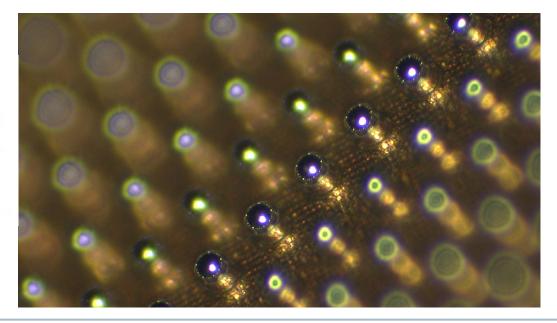

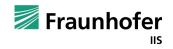

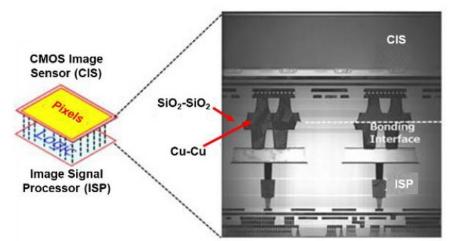

#### **Hybrid Bonding**

- Also known as direct bond interconnect (DBI)

- Either Wafer2Wafer, Die2Wafer or Die2Die

- Optimizing CMP condition main factor to create suitable surface

- First image sensors using W2W

- Pitch currently 1-2u for W2W and ~10u for D2X

4-high cross section

#### 50um die stacked 4-high

CHIPLET

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

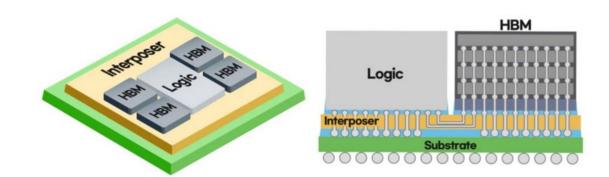

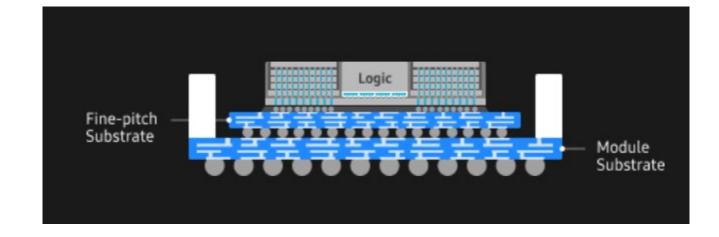

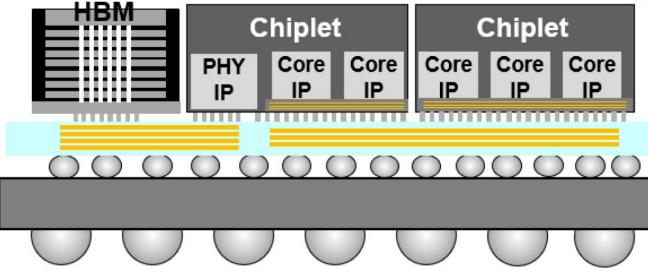

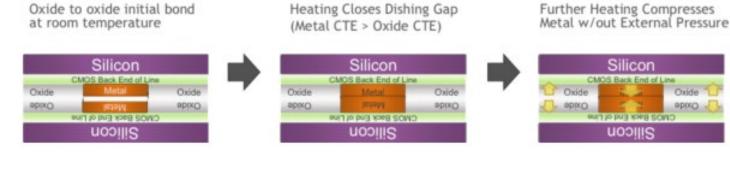

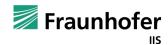

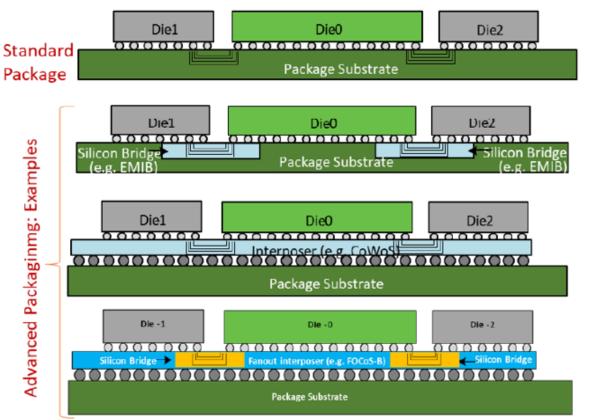

#### **Interposer or 2.5D Integration**

- Either RDL interposer or silicon interposer depending on system requirements

- High volume expected to be on silicon interposer due to better performance but higher cost (especially on design side)

- Organic or RDL interposer expected more in mid-volume due to more flexibility and easier design usage (in terms of signal and power integrity)

- Supported by many vendors

- Arising option to embedded capacitors as MiM or deep-trench capacitor to allow decoupling or basic capacitance function, that are more expensive on ICs

- Expected almost-passive interposers (with very few active parts on specialized technologies) in upcoming years

January 24 - 26, 2023

ChipletSummit.com

DoubleTree by Hilton San Jose

https://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=9684894

Annual Update on Packaging

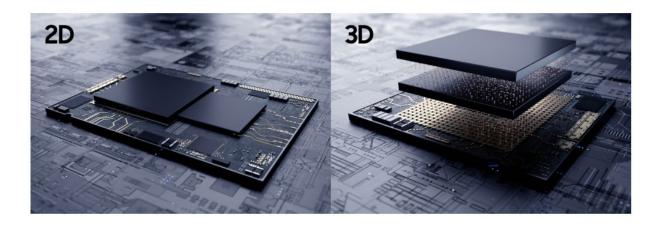

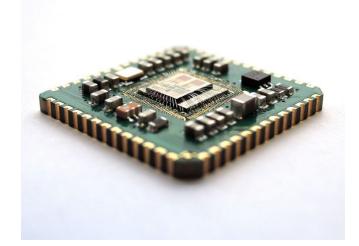

#### **3D Integration**

- Multiple variants

- Form stacked dies using wirebonds

- Package-on-Package (e.g. Smartwatch)

- 3D IC Stacking

Annual Update on Packaging

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

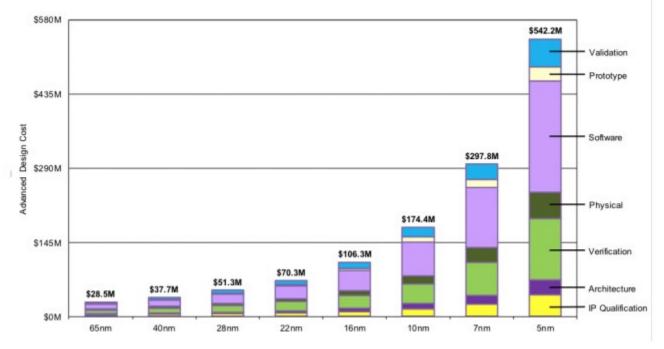

#### Chiplets

- Cost perspective

- Development cost show large rise with going to smaller nodes

- Chiplets are one way to reduce this cost by not transferring all functionality to smaller nodes

https://www.extremetech.com/computing/272096-3nm-process-node

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

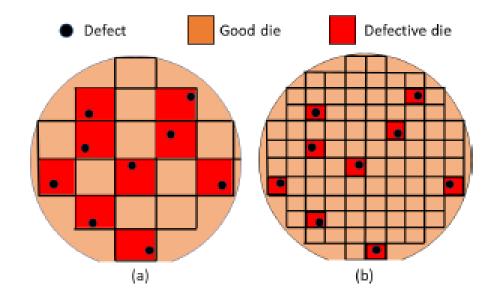

#### Chiplets

- Yield perspective

- Currently most defective dies are coming from spot defects

- Spot defects have a known probability for known processes

- Large SoC suffer more from spot defects

- Therefore yield per wafer could be increased by reducing die size

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

#### Chiplets

- Packaging perspective

- Chiplets could gain advantage by all the available packaging options presented

- Many available options

- ->many potential system solutions

- -> new applications enabled

- Xilinx was one of the first due to regularity of FPGAs and therefore good scalability

- Multi-core CPUs are to follow

- Separation of core and memory

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

#### Chiplets

- Interoperability

- Most current system are using components from one vendor

- To combine small functional blocks from different. vendors, standardized interfaces are required

- Like UCIe driven by Intel

- Bunch-of-Wires or Open HBI

- Most of the proposed interfaces are scalable in terms of IC pitch and package technology used

Universal Chiplet Interconnect Express (UCIe)®: Building an open chiplet ecosystem

January 24 - 26, 2023 **DoubleTree by Hilton San Jose** ChipletSummit.com

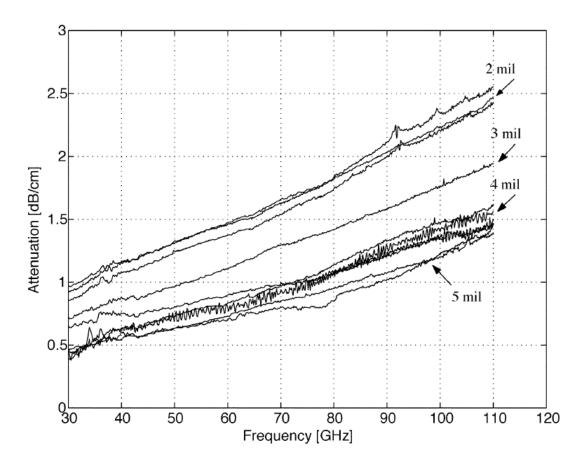

#### Materials

- Package developments are also related to material development

- One main driver is higher speed for signal transmission and wireless applications

- This brings the demand for materials with low-loss dissipations factor and low dielectric constant like liquid crystal polymer (LCP)

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com Annual Update on Packaging

#### Roadmap

• For organic substrates

#### for silicon-based integration

https://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=9684894

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

## **Summary**

Packaging is a market with rising market size

- Large amount of investments ongoing to create capabilities and volume

- Many packaging solutions available for mass production

- Diversity and many options available

- Many of the solutions are expected to be apparent the next years

- No technology foreseen to rule out all other

January 24 - 26, 2023 DoubleTree by Hilton San Jose ChipletSummit.com

## Contact

Andy Heinig Head of Department Efficient Electronics Tel. +49 351 45691-250 andy.heinig@eas.iis.fraunhofer.de

Fraunhofer Institute for Integrated Circuits IIS Division Engineering of Adaptive Systems EAS Münchner Straße 16 01187 Dresden; Germany www.eas.iis.fraunhofer.de Fabian HopschAdvanced System IntegrationTel. +49 351 45691-263fabian.hopsch@eas.iis.fraunhofer.de

Contact

Fraunhofer Institute for Integrated Circuits IIS Division Engineering of Adaptive Systems EAS Münchner Straße 16 01187 Dresden; Germany www.eas.iis.fraunhofer.de