### SYNOPSYS®

## UCIe: An Open Standard Interface for Chiplet-Based Multi-Die Systems

Manuel Mota Sr. Product Marketing Manager, Synopsys January, 26<sup>th</sup> 2023

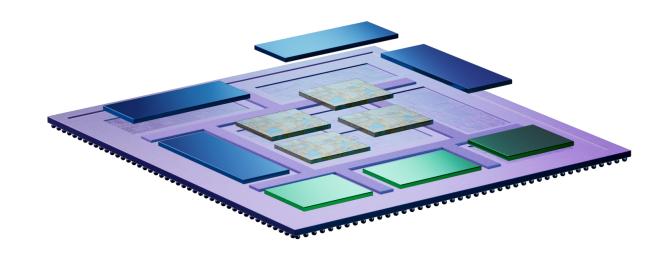

# The SysMoore Era of Multi-Die Systems

### The Era of Multi-Die Systems is Here

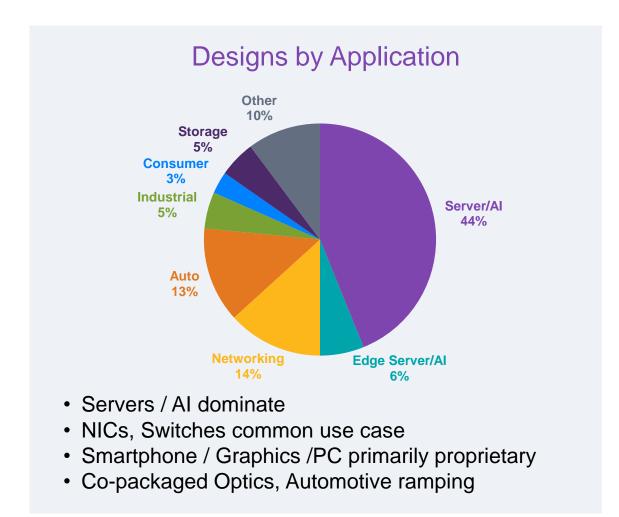

Synopsys Tracking ~100 Multi-Die System Designs

### Multi-Die System Drivers

Accelerated scaling of system functionality at a cost-effective price (>2X reticle limits)

Reduced risk & time-to-market by re-using proven designs/die

Lower system power while increasing throughput (up to 30%)

Rapid creation of new product variants for flexible portfolio management

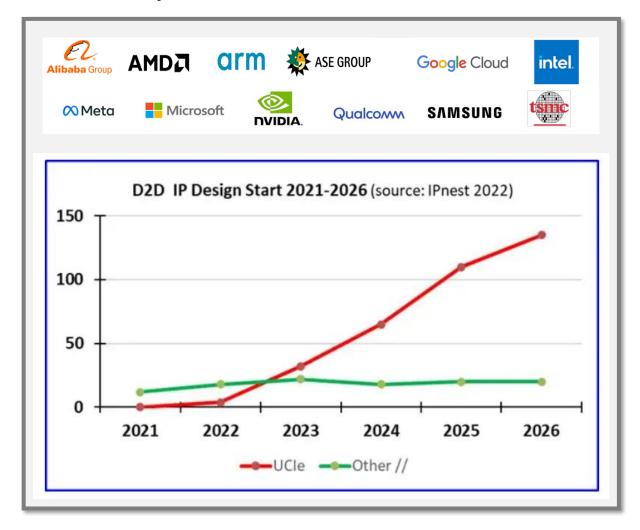

### Multi-Die Systems Require D2D Interface Standardization

Technical Merits, Maturity & Strength of Ecosystem are Key for Success

| Alliance               | OIF                             | OPEN<br>Compute<br>Project® |                                    | CHIPS ALLIANCE     | Universal Chiplet<br>Interconnect Express          |

|------------------------|---------------------------------|-----------------------------|------------------------------------|--------------------|----------------------------------------------------|

| Standard               | XSR                             | BOW                         | ОНВІ                               | AIB                | UCle                                               |

| Data Rate              | 112G / 224G                     | 8G / 16G                    | 8G / 16G                           | 6G                 | 16G / 32G                                          |

| Protocol               | Not Defined                     | Not Defined                 | Not Defined                        | Not Defined        | Streaming,<br>PCIe, CXL                            |

| Package<br>Focus       | 2D                              | 2D<br>(2.5D also supported) | 2.5D<br>(2D also supported)        | 2.5D               | 2D, 2.5D                                           |

| Target<br>Applications | Optical Networking<br>(CPO/NPO) | Cost sensitive aggregation  | High density scale for data center | Mil-aero ecosystem | Scale & Split w/ streaming Aggregation w/ PCIe/CXL |

### UCle is the Preferred D2D Interface

Technical Merits, Comprehensive Spec & Broad Eco-System

- Technical Merits

- Most compelling PPAs

- Comprehensive & Futureproof

- Full stack & Interoperability

- Broad Industry Support

- Open Eco-system

- More than 100 UCle members

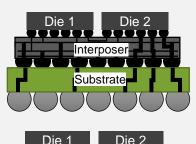

### UCIe PHY Support for Advanced/Standard Packages

### Two Options Optimized for Each Use Case

### **UCIe-A PHY for Advanced Packages**

- 1Tbps per module @ 16Gbps/pin

- 0.3pJ/bit energy efficiency

- 64 TX + 64 RX pins per Module

- 5.2Tbps/mm aggregate BW efficiency

- 45~55um bump pitch

- 2mm unterminated link

- Low power modes

- 2ns latency (TX + RX)

- BFR << 1e-15</li>

### **UCIe-S PHY for Standard Packages**

- 0.25Tbps per module @ 16Gbps/pin

- 0.5pJ/bit Energy Efficiency

- 16 TX + 16 RX pins per Module

- 0.9Tbps/mm aggregate BW efficiency\*

- 110~130um bump pitch

- 25mm, terminated link

- Low power modes

- 2ns latency (TX + RX)

- BFR << 1e-15

- \* 32 pin stacked mdule

Common Architecture, Protocol and Logic Interfaces for all Package Types

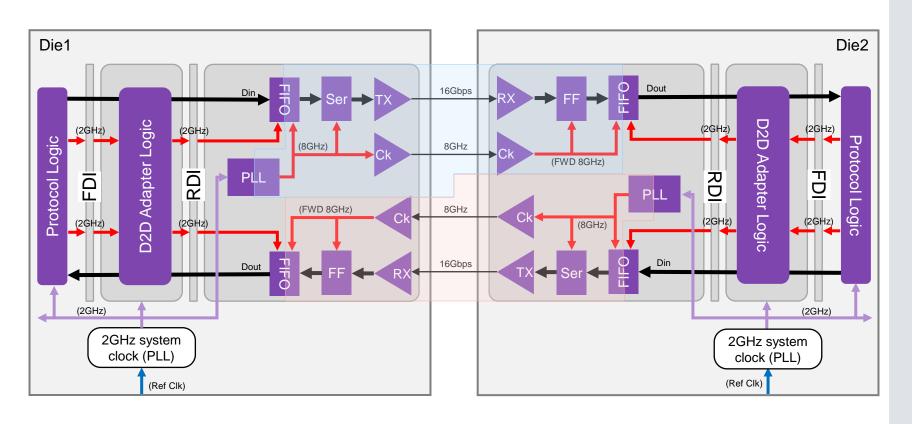

### UCIe is a Latency Optimized Architecture

Simplified Clock Domains w/ Clock Forwarding and Matched Lanes

- Optimized architecture for D2D links

- No CDR

- Simple equalization

- Optional RX termination

- RDI/FDI interface operate with local 2GHz system clock

- Optionally 1GHz

- PHY includes FIFOs to accommodate phase mismatch between 8GHz FWD clk and local clk

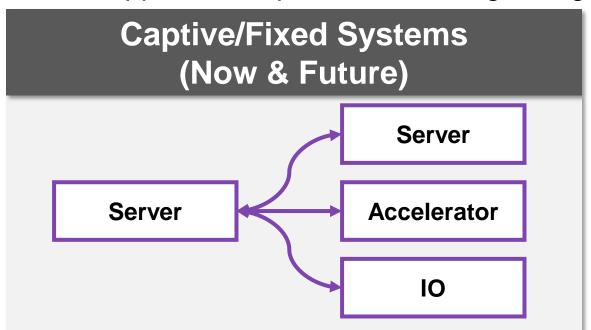

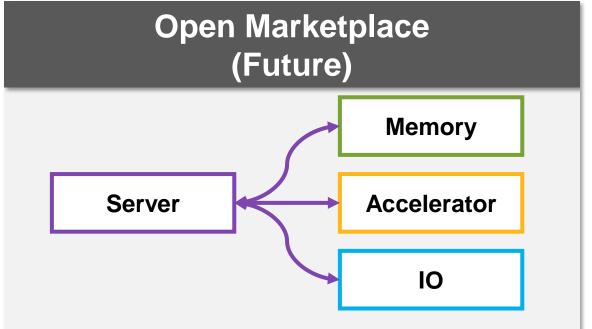

### Use Models Projected to Evolve from Captive → Marketplace

UCle Supports Multiple Protocols: Lightweight (Captive) & Standards Based (Chiplets)

- Function splitting by the same vendor

- No interop, no standard protocol

- Lightweight, low latency, streaming mode

- Bridges to NoC for virtual NoC-NoC interface

- Example Server, Smart NIC, AI, Switches

- Isolated functions from different vendors

- Standardization, eco-system & Interop

- Protocols: CXL & PCIe

- Example Chiplets, Memory extension, 5G

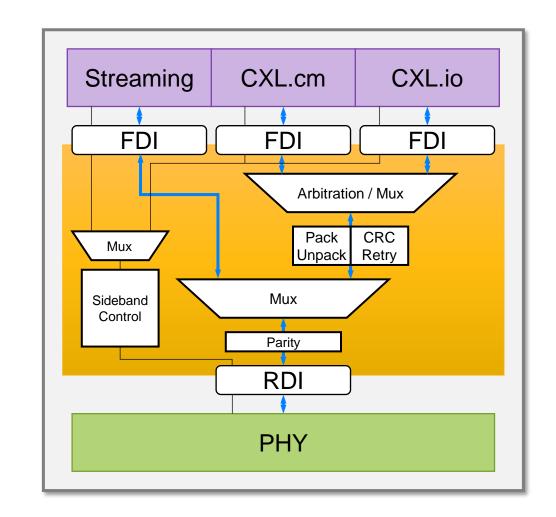

### Muti-Protocol Selection Enabled by UCIe

For General Purpose "Market Place" Chiplets

- Negotiation of protocol at link startup

- Reliable data transfer

- CRC computation and Retry functionality

- Protocol Arbitration and Muxing

- Link State Management

- SideBand channel for

- Protocol and Parameter negotiation with the remote Link partner

- Supporting various flit modes

- Eg: CXL & PCIe 256B Flit and CXL 68B Flits

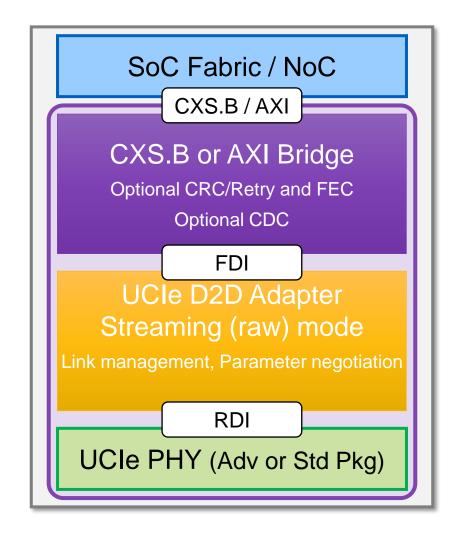

### Lightweight Multi-Die NoC-NoC Bridge with UCIe

Protocol Bridge to FDI Leveraging Streaming Mode

- Low complexity D2D interconnect for compute-compute links

- Ultra Low Latency down to ~5.5ns Fabric-to-Fabric

- Supports coherent and non-coherent data traffic

- High link Reliability with CRC / Retry functionality

- Optional FEC coding minimizes BER and Retry rate, enables predictable latency links

- Optimized for Compute-Compute links in Scaling & Die Splitting use cases

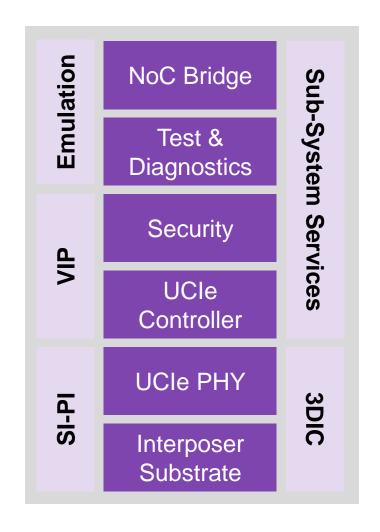

### Synopsys UCIe Interface Solution

Lightweight Die-to-Die Interface for Multi-Die Systems

- Latency and Power Optimized PHY and Controller

- Support for all package technologies

- Extensive test & debug features for KGD

- Protocol stack options optimized for all use cases

- Interface to common fabric interfaces

- CXL protocol → CXL fabric (.mem/cache) or AXI fabric (.io)

- PCle6 protocol → AXI fabric

- Streaming: CXS.B or AXI bridge → CXL or AXI fabric

- Design Enablement with VIP, Emulation, Services, Design Tools

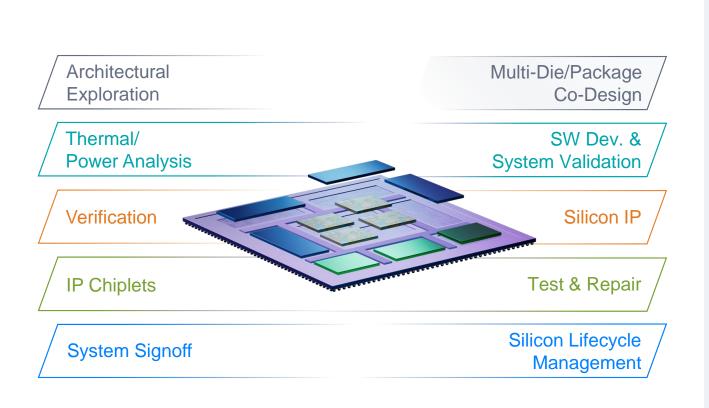

### Synopsys Multi-Die System Solutions

### A Comprehensive Solution for Heterogeneous Integration

Optimize thermal, power, Architectural and performance with early **Exploration** exploration and partitioning Rapid software development Software Dev. and validation with high-capacity & Validation emulation & prototyping Efficient die/package co-design Design with unified exploration-to-signoff Implementation platform and robust IP Improve health, security and Manufacturing reliability with holistic test and & Reliability

lifecycle management solutions

SYNOPSYS<sup>®</sup>

### Thank You