# Using Silicon Photonics in a Co-Packaged Optical Interconnect

Manish Mehta

VP of Marketing and Operations – Optical Systems Division

February 6th, 2024

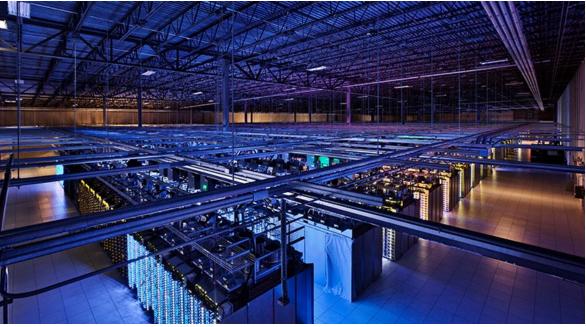

### **Datacenters: Systems At Scale**

\$100B Annual Capex Spend by Cloud with 15% CAGR<sup>1</sup>

19.5 Zettabytes of Cloud Data Movement<sup>2</sup> Per hyperscale datacenter

- > 100k Servers

- > 10k Switches

- > 1M Optical Interconnects

#### Source:

- 1. 650 Group, Cloud Total Market and Forecast Report

- 2. Cisco Global Cloud Index, https://blogs.cisco.com/news/acceleration-of-multicloud-era

- 3. Left: Digital Realty's Loudoun Three campus in Ashburn, Virginia. Photo courtesy of Digital Realty

- 4. Right: Google's Council Bluffs, Iowa Data Center. Photo courtesy of Google

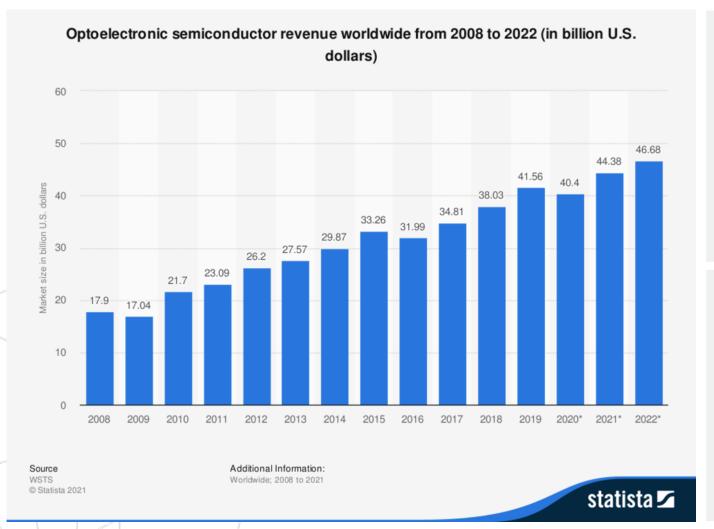

### The Increasing Role of Photonics Within Semiconductors

- Markets and Markets, Silicon Photonics Market with COVID-19 Impact Analysis by Product

- 2. Emgen Research

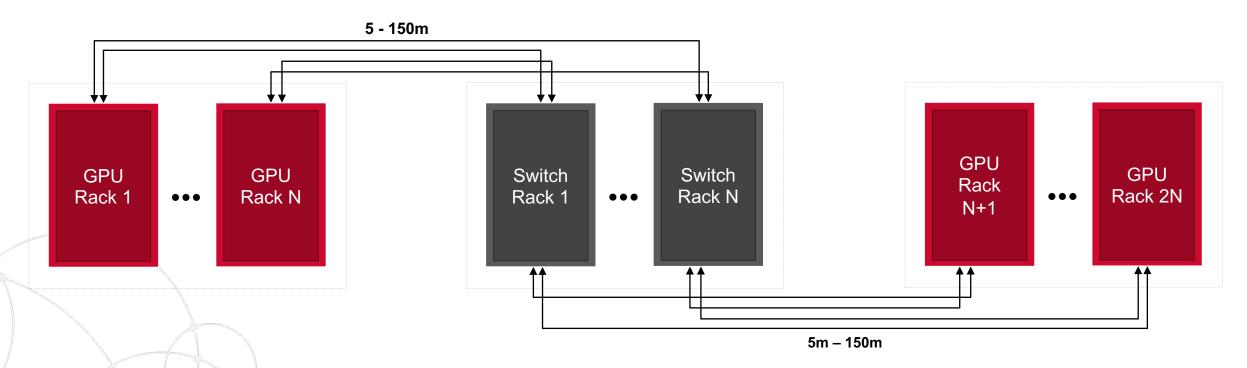

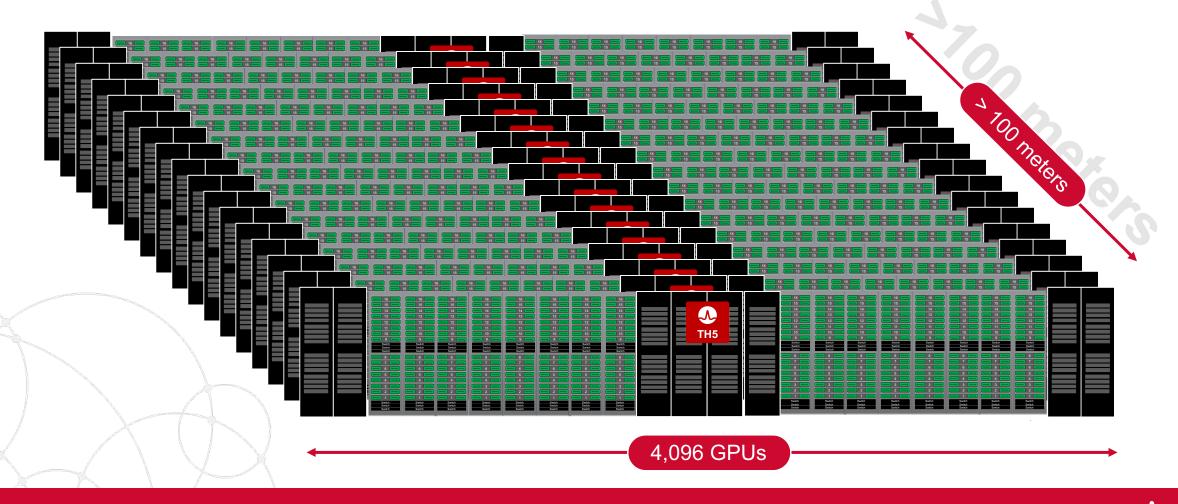

#### **Al Cluster Trend: Interconnect Distances**

#### Increased distance from GPU Rack to Switch Rack

Clusters > 32k GPUs in deployment Difficult for copper interconnect to support GPU clusters larger than 64

Single-mode optics needed for speeds > 106Gbps and distances > 100m

Multi-mode optics could be used to support 106Gbps at < 100m

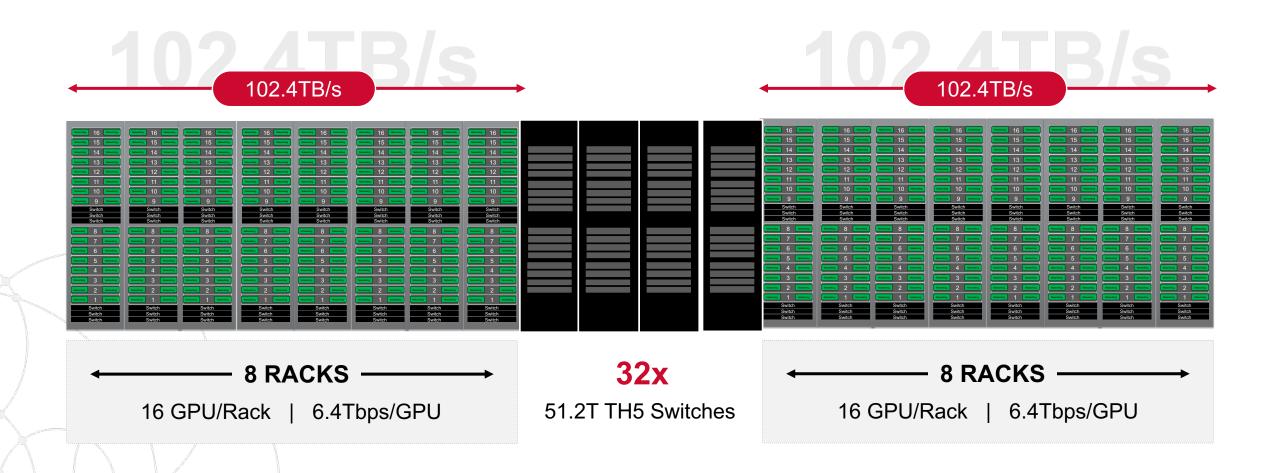

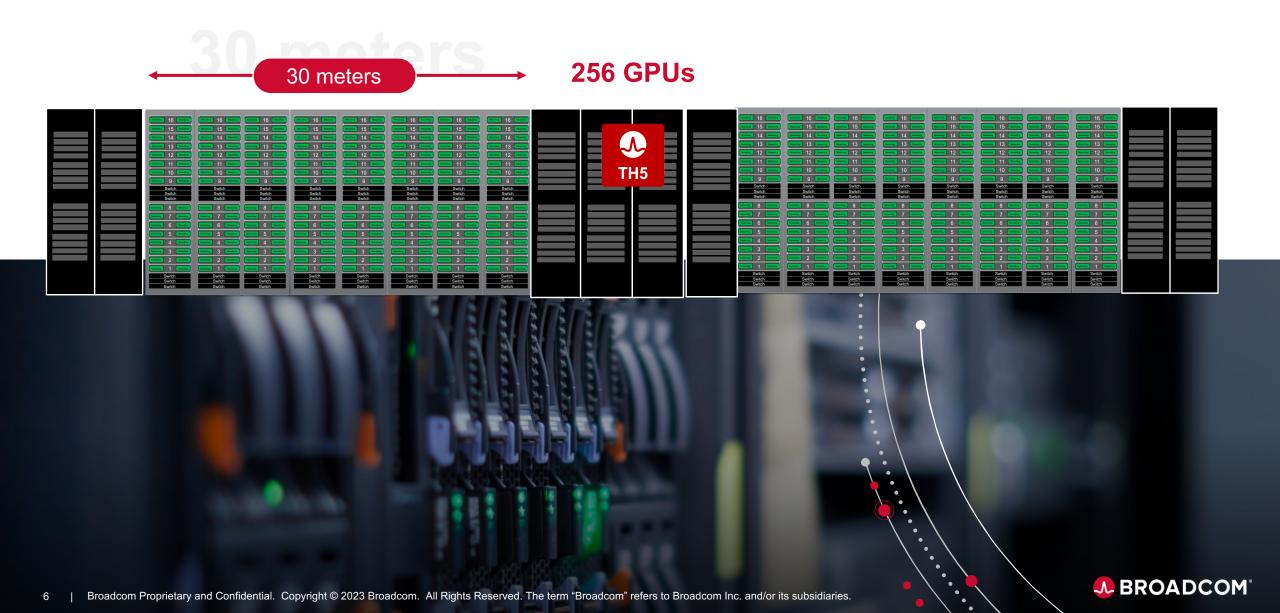

### Al ML Cluster Example: 256 GPUs with 51.2T Switches

### Al ML Cluster Example: Scale-out

### Al ML Cluster Example: Scale-out

#### **Optical Interconnect required between GPU pods**

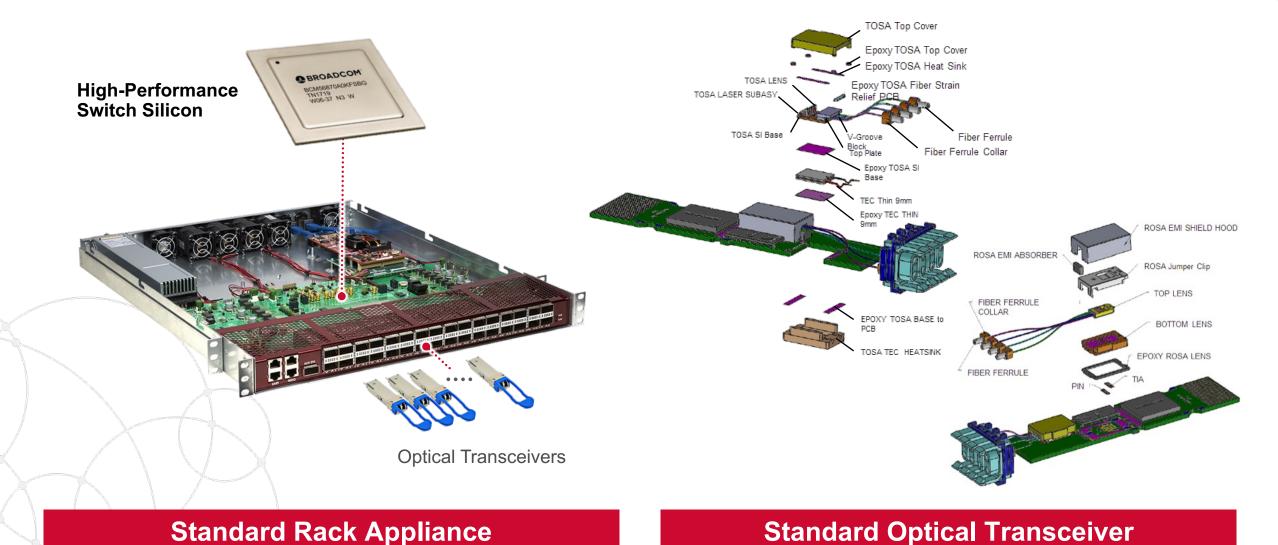

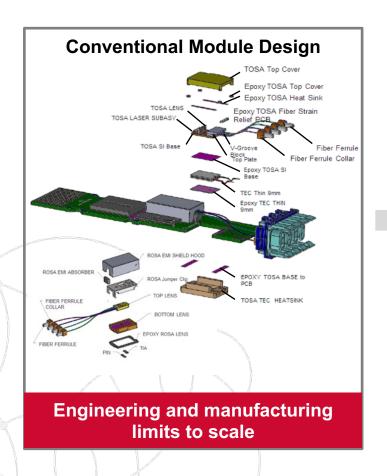

### **Complexity of Each Box in the Datacenter**

**<b>№** BROADCOM<sup>®</sup>

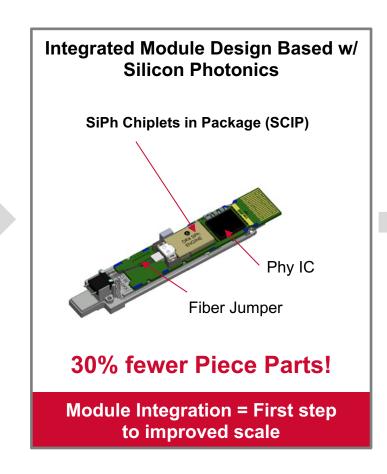

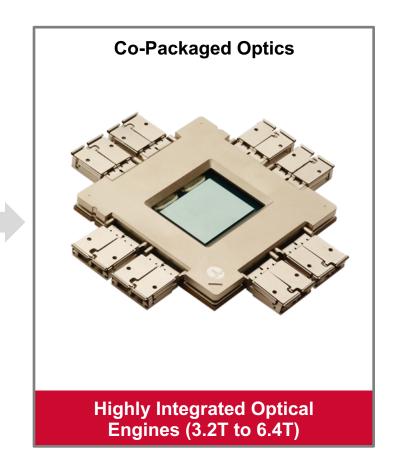

### **Evolution of Optics: Discrete III-V to Co-Packaged SiPh**

### True Co-Packaged Optics Using Heterogenous Integration

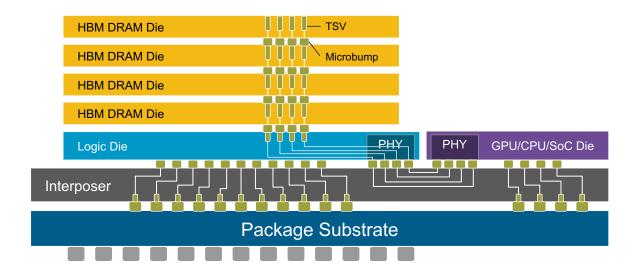

### **Co-Packaging**

- Integration of multiple dies on a common package substrate

- High volume use cases today like HBM

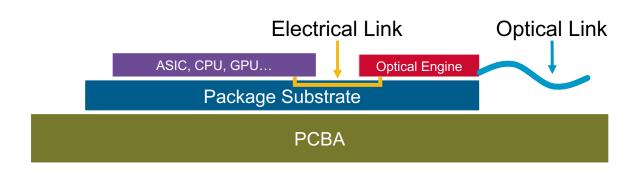

### **Co-Packaged Optics**

- Integration of optical engines on a common package substrate

- Objective: alleviate the "interconnect density bottleneck"

<sup>\*</sup> Source: Image, AMD, https://www.amd.com/en/technologies/hbm

<sup>\*</sup>Source: Yole Developpement, <a href="http://www.yole.fr/3D">http://www.yole.fr/3D</a> 25D Stacking Technologies IntelEMIB.aspx#.YJyx7pNKh25

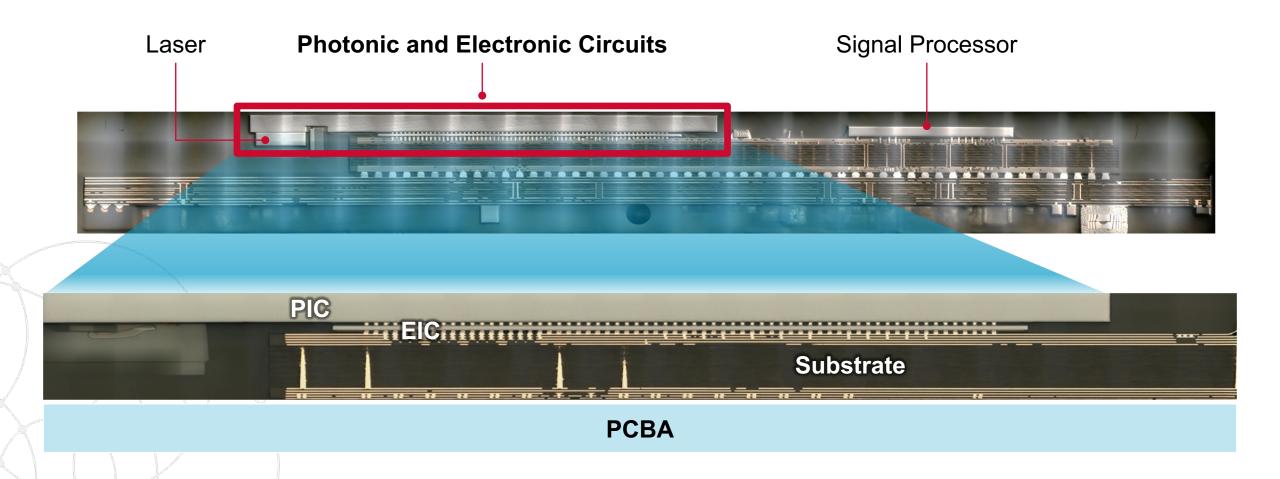

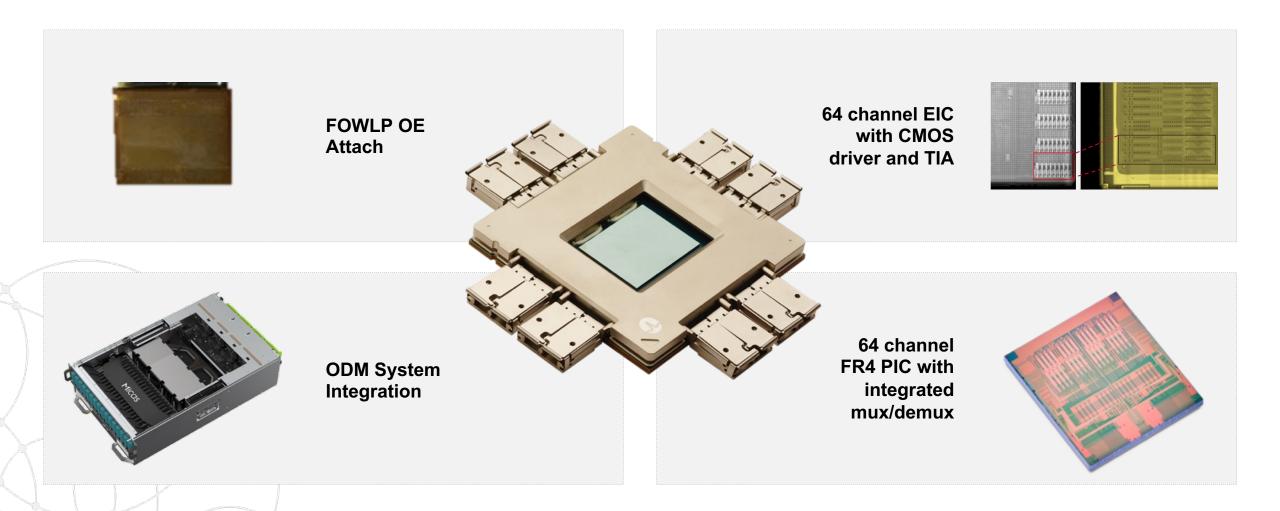

### The Anatomy of a Fully Integrated Silicon Photonics Engine

### **Overcoming Copper Bottlenecks at Scale**

#### **ASIC**

- Core switch,

SerDes and DSP in leading node

- Sustained generational differentiation

# Mixed Signal IC

Power and performance optimized in both SiGe and CMOS

## Optical Devices & Fabs

- 50M lasers/year from internal fabs

- High-volume optical manufacturing

- High-power, multi-wavelength sources

# Advanced Packaging & Test

- Wafer-level test

- TSV

- FoWLP

## Silicon Photonics

- High-density PIC design

- Modulators and PDs in silicon

- Low-loss SOI waveguides

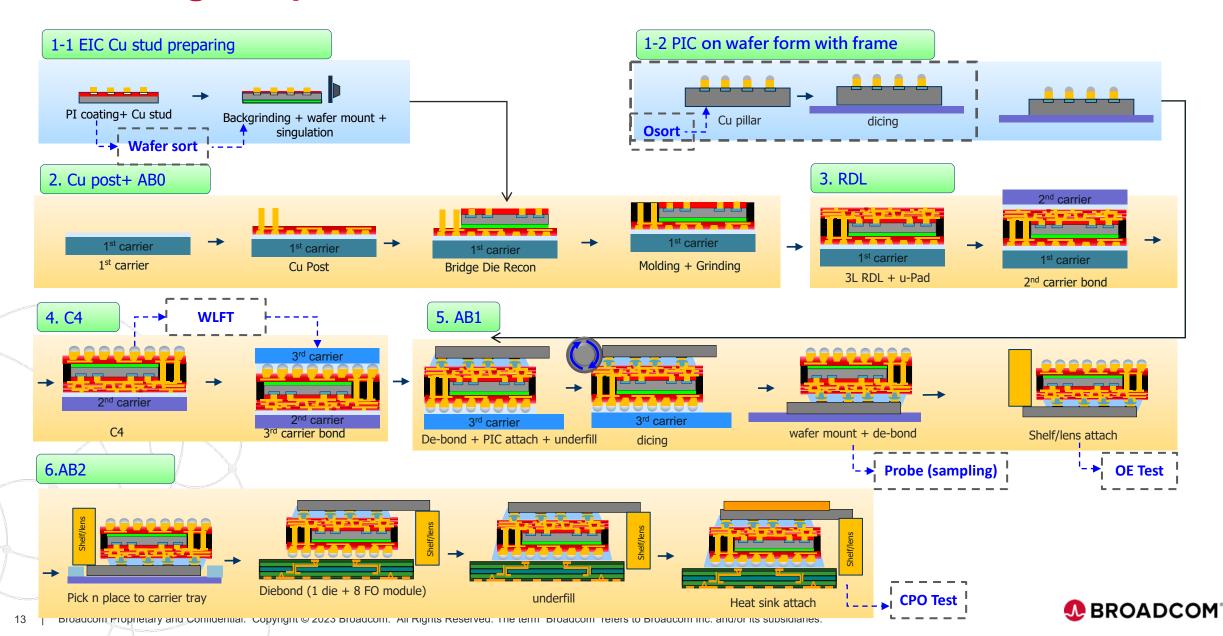

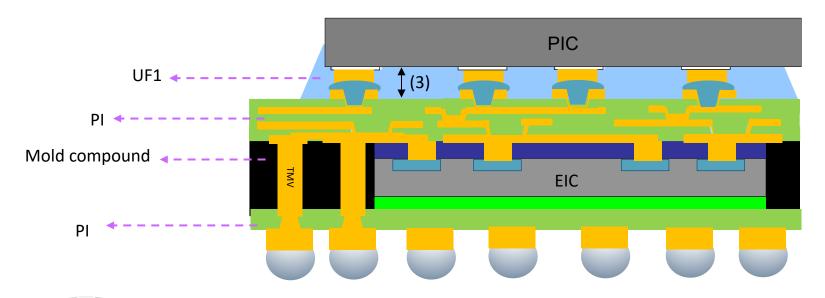

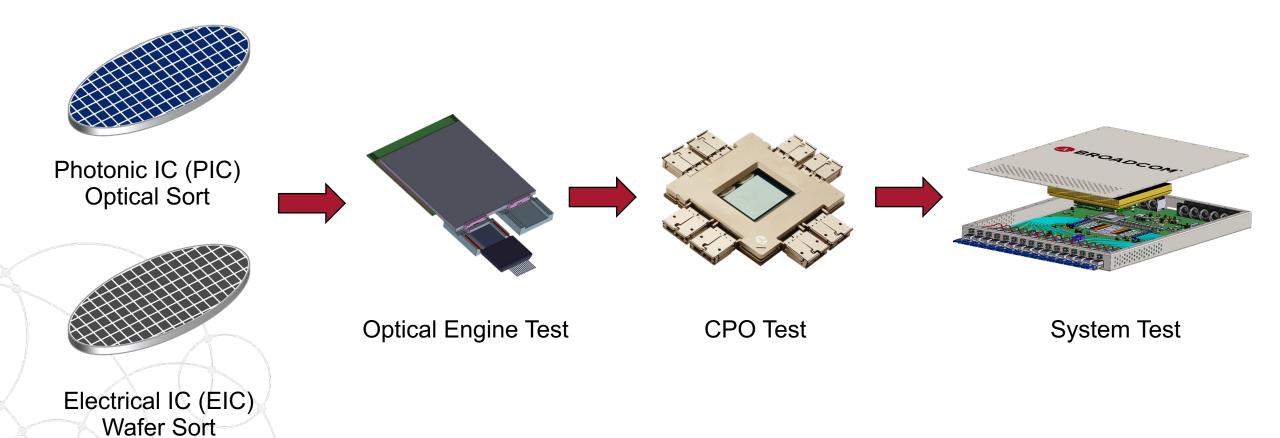

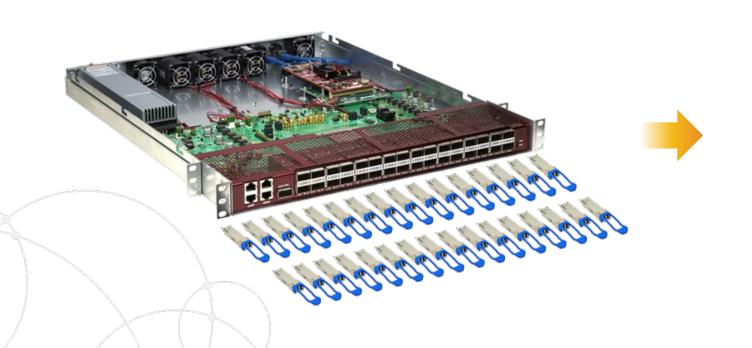

### **Co-Packaged Optics Fan-Out Process Flow**

### **Optical Engine Structure**

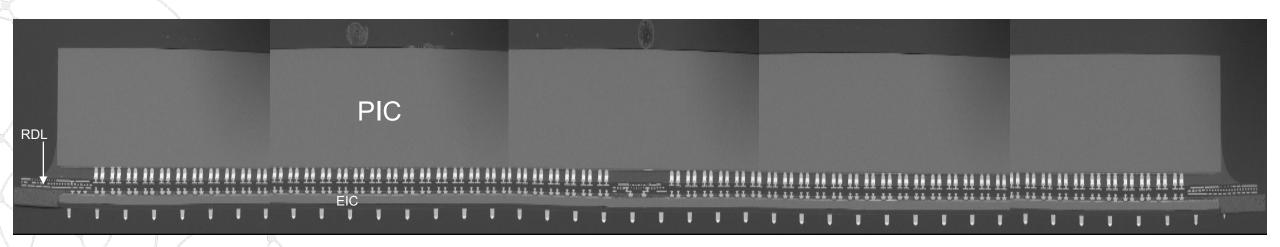

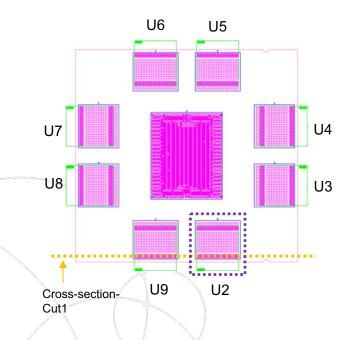

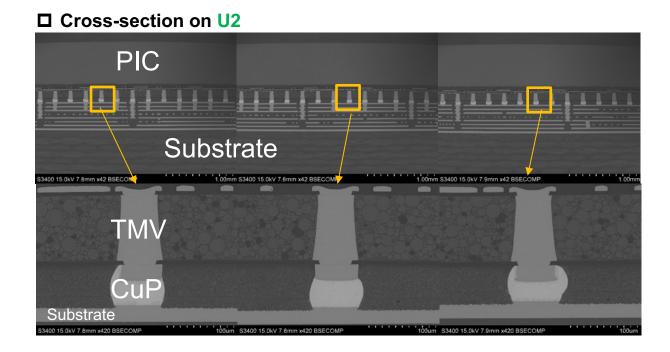

### **Optical Engine Cross-section Images**

### **Test Point Insertion**

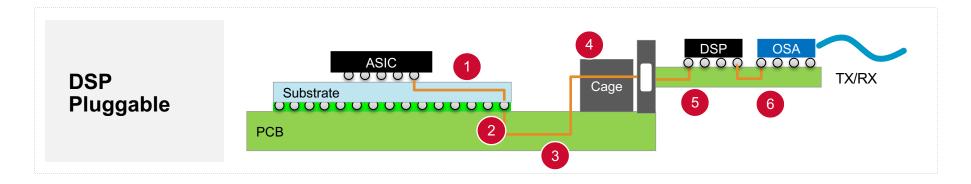

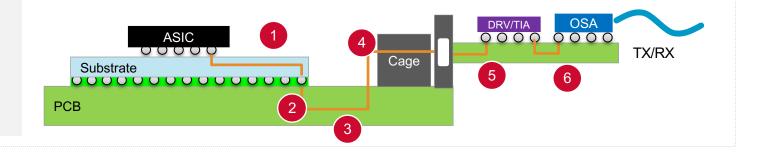

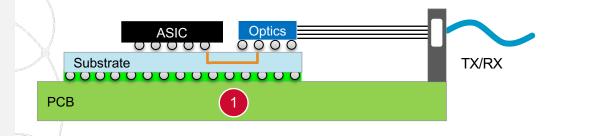

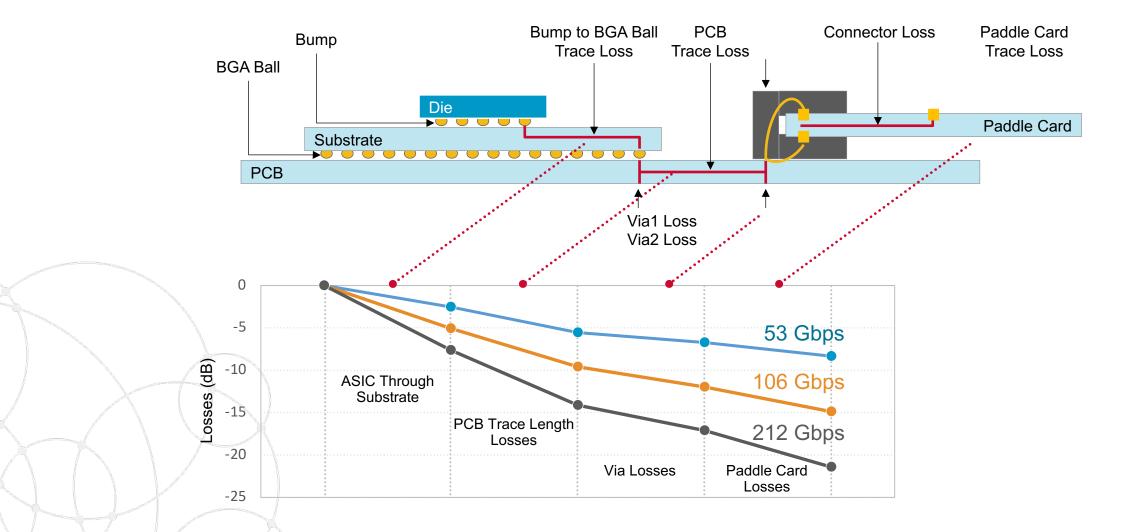

### **CPO Insertion Loss Savings vs. Pluggables**

LPO Pluggable

**CPO**

>30% Cost Savings

>12dB

Insertion Loss savings

- 1 ASIC through substrate

- 2 Via Losses

- 3 PCB Trace Loss

- 4 Connector Losses

- 5 Module PCB Losses

- 6 OSA Interconnect loss

### **Copper I/O Approaching a Limit**

### **Optimizing Electrical to Optical Conversion Efficiency**

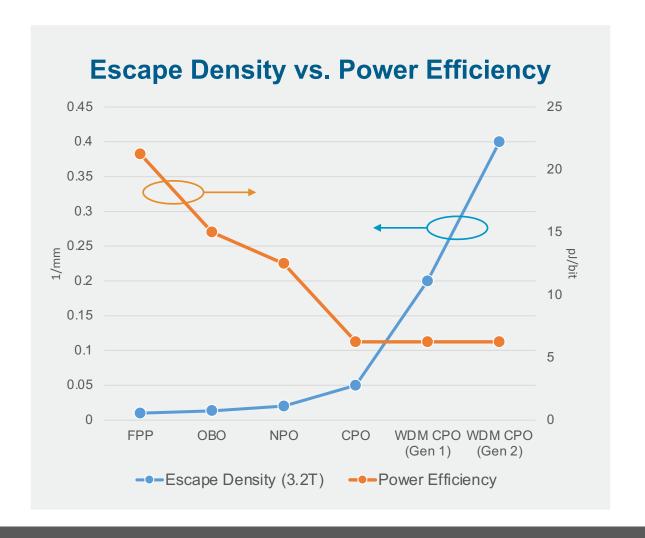

**Exponential Benefit in I/O Escape Density and Power Density with Immediate Conversion**

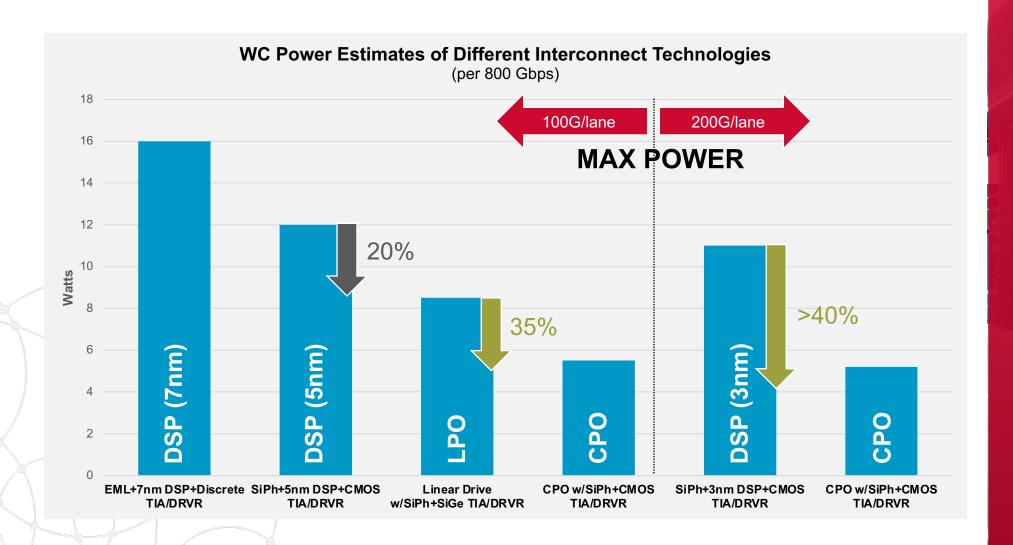

### **CPO Power Savings vs. Pluggables**

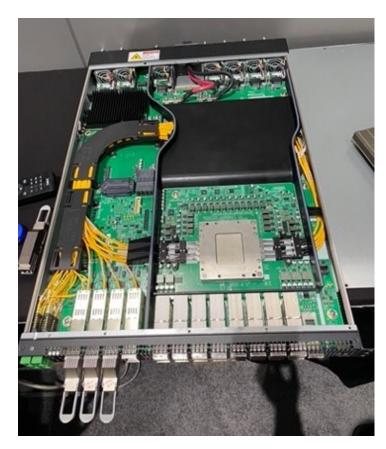

### **TH5-Bailly CPO: Sampling**

### System Level Simplification Using Co-Packaged Optics

Signification reduction in board and system complexity

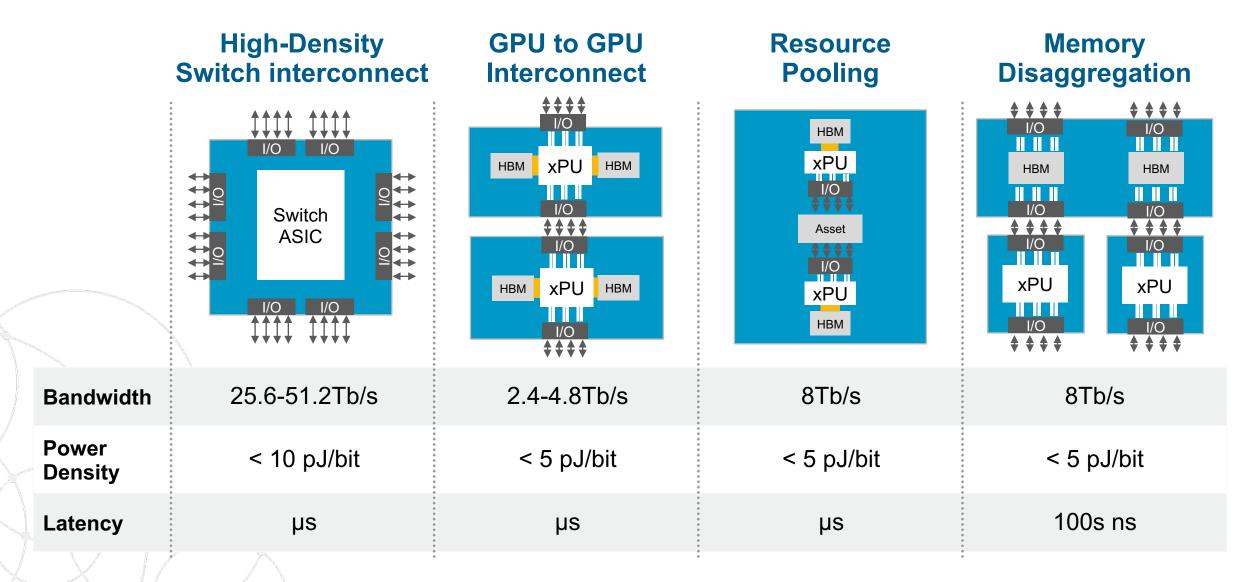

### **Architectural Migrations Leveraging I/O Bandwidth**

### **Thank You**