## Model-Based System Design for Chiplet-Based Architectures

Denis Dutoit – CEA List Program Manager – Advanced Computing

- Advanced packaging and demonstrators at CEA

- Chiplet platform for AI at Edge

- System-of-chiplets for Automotive

- Model-based system design

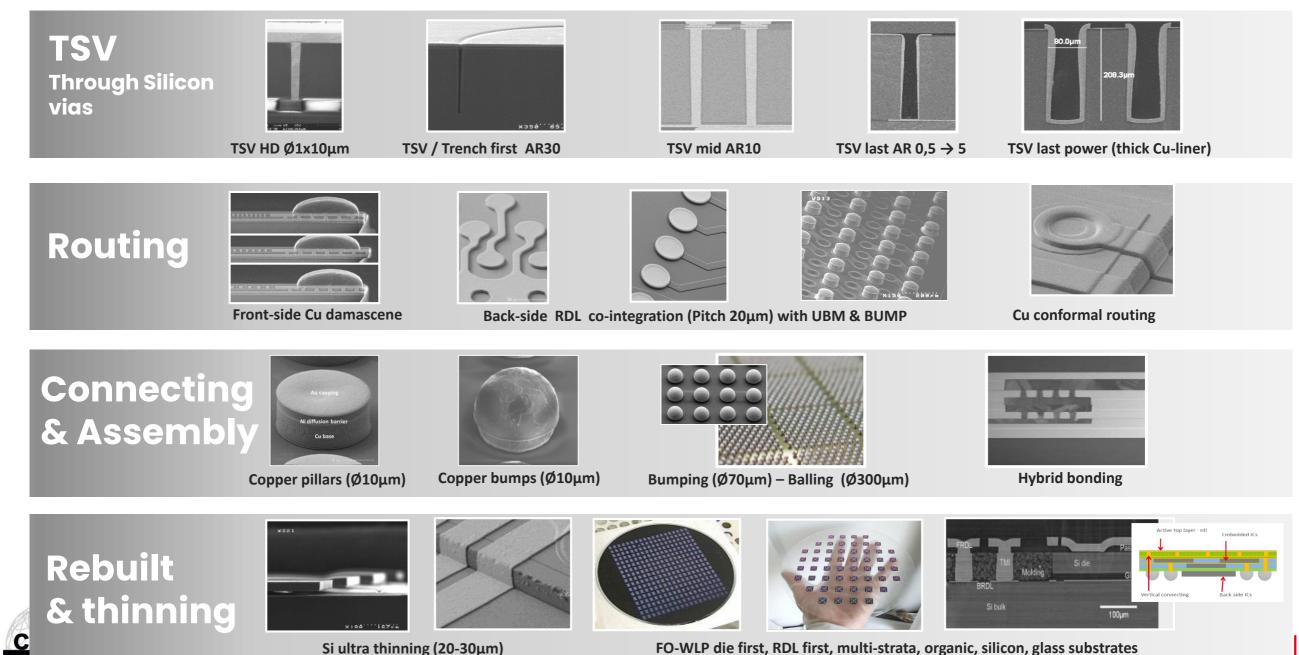

### Advanced packaging and demonstrators at CEA

February 6-8, 2024 Santa Clara Convention Center ChipletSummit.com <u>cea</u> list

### A complete tool box ...

#### **CEA tool box**

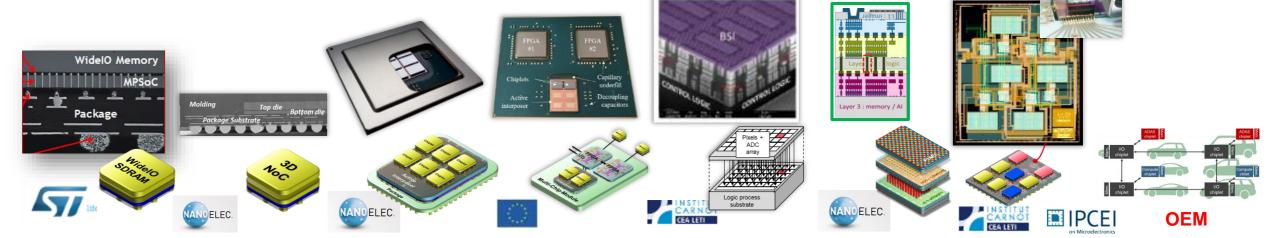

#### ... to leverage chiplet-based architectures.

| 3D Circuit                    | WIOMING                                         | 3DNOC                                    | INTACT                                                  | EXANODE                                                                            | RETINE                                                           | SMART IMAGER                                      | HUBEO-STARAC                                                                                                               | THIS TALK                                                                                                  |

|-------------------------------|-------------------------------------------------|------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Application &<br>Architecture | 4G Telecom BB<br>WIDEIO DRAM<br>Memory-on-Logic | HPC<br>2 layer 3D NOC<br>Logic-on-Logic  | HPC:<br>96 Cores,<br>6 Chiplets on<br>active interposer | HPC<br>Heterogeneous<br>chiplets, 2<br>chiplets, 1 active<br>interposer, 2<br>FPGA | IMAGER<br>2 layer BSI,<br>Distributed Pixel<br>clusters on Logic | IMAGER<br>3 layer BSI,<br>In Sensor Al<br>engines | <ul> <li>HPC:</li> <li>1Tb/s/mm2 link</li> <li>6 Chiplets on photonic NoC &amp; interposer, E-O-E TX-RX chiplet</li> </ul> | AUTOMOTIVE:<br>Model-based<br>design,<br>Heterogeneous<br>chiplet, 1 I/O<br>chiplet, 2 compute<br>chiplets |

| CMOS<br>technology            | DRAM + 65nm                                     | 65nm + 65 nm                             | FD28nm + 65nm                                           | FD28nm + 65nm<br>+ FPGA                                                            | 130nm                                                            | IMG +<br>FD28 + FD28nm                            | 100nm SOI SiPho,<br>FDSOI28nm                                                                                              | Heterogeneous                                                                                              |

| 3D<br>Technology              | TSV & Cu-pillar<br>(40 µm pitch,<br>F2B)        | TSV & Cu-pillar<br>(40 µm pitch,<br>F2B) | TSV & Cu Pillar<br>(20 µm pitch,<br>F2F)                | TSV & Cu Pillar<br>(20 µm pitch,<br>F2F)<br>MCM                                    | W2W, F2F,<br>Hybrid Bonding                                      | TSV 2 µm pitch,<br>W2W2W, Hybrid<br>Bonding       | Cu-Pillar, TSV<br>middle, Photonic +<br>3D integration                                                                     | System-In-<br>Package,<br>advanced<br>substrate                                                            |

| Status                        | Silicon<br>[VLSI'2013]                          | Silicon<br>[ISSCC'2016]                  | Silicon<br>[ESSCIRC'2018]<br>[ISSCC'2020]               | Silicon<br>[VLSI'2020]                                                             | Silicon<br>[VLSI'2018]                                           | On-going design<br>[VLSI-TSA'2022]                | Silicon<br>[ISSCC'18]<br>On-going fab'<br>[DATE'2020]                                                                      | Concept<br>[This Talk]                                                                                     |

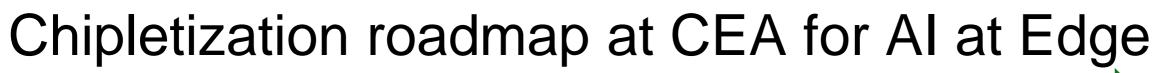

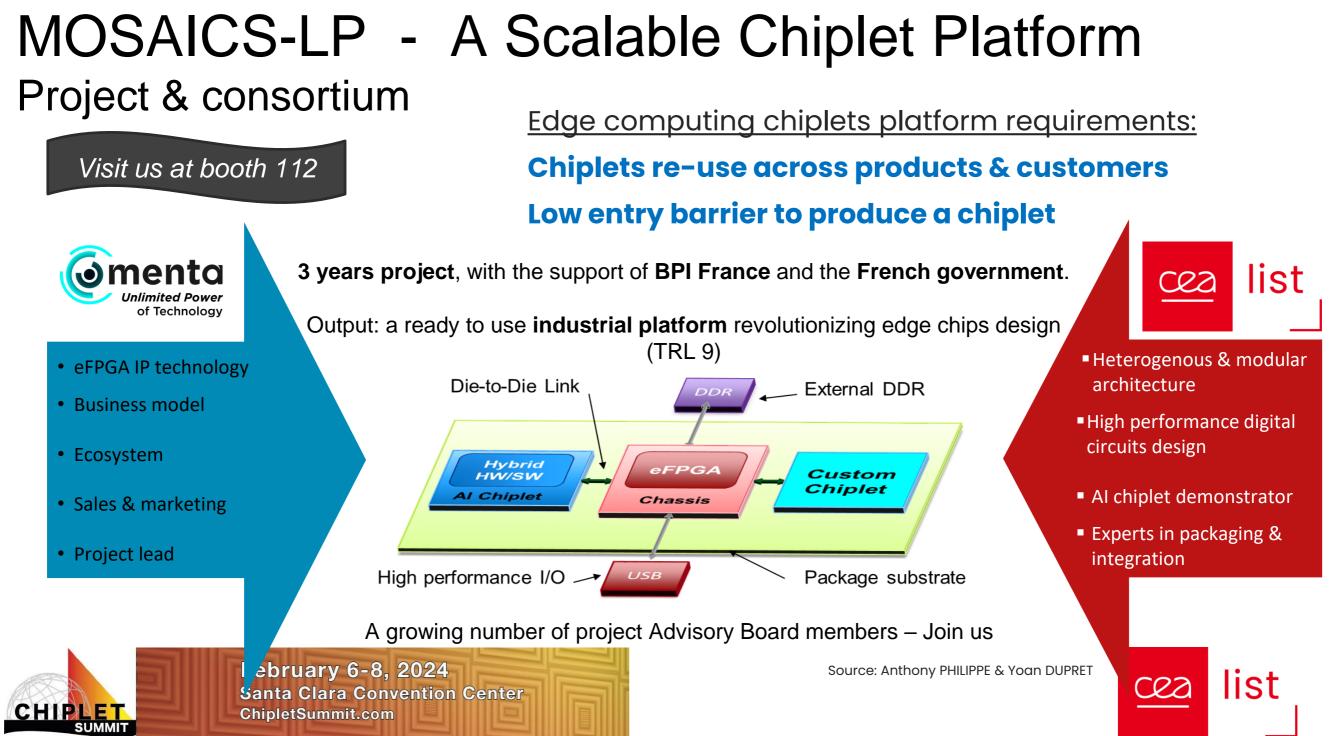

### Chiplet platform for AI at Edge

February 6-8, 2024 Santa Clara Convention Center ChipletSummit.com <u>cea</u> list

#### System-of-chiplets for Automotive

February 6-8, 2024 Santa Clara Convention Center ChipletSummit.com <u>cea</u> list

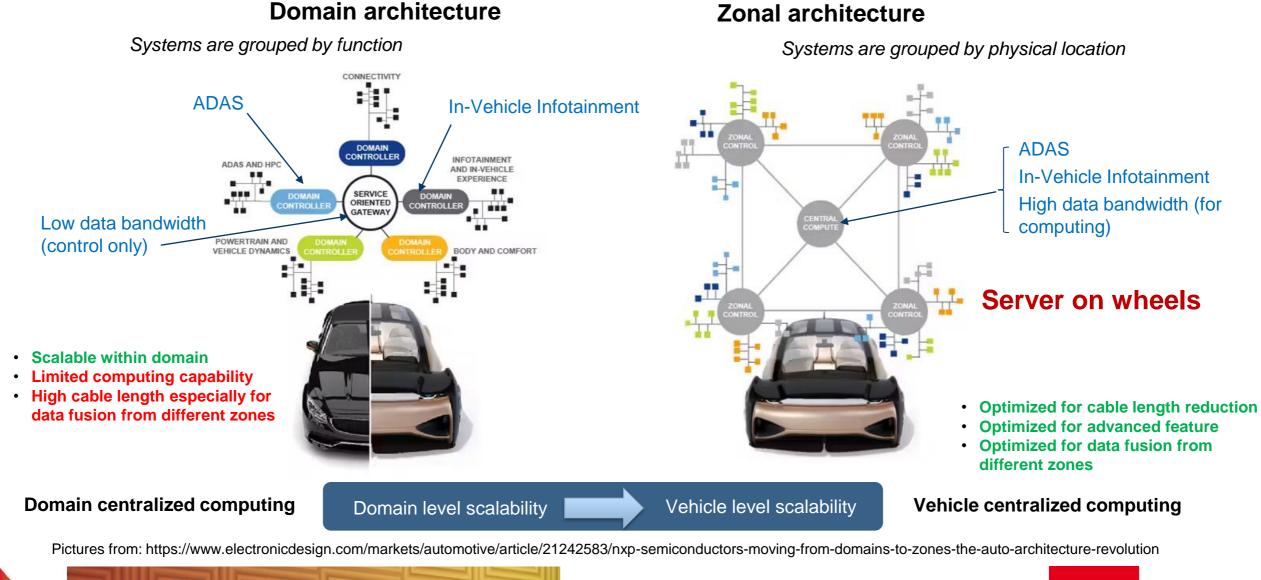

#### The auto architecture revolution: moving from domains to zones

February 6-8, 2024 Santa Clara Convention Center ChipletSummit.com

Model-Based System Design for Chiplet-Based Architectures – D. Dutoit

list

CQA

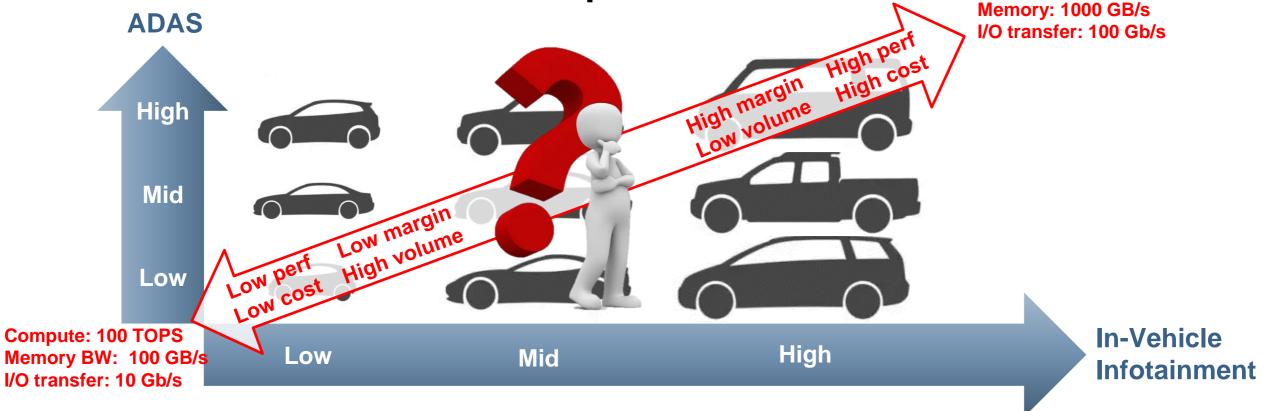

# Vehicle level scalability: performance continuum over the vehicle line-up

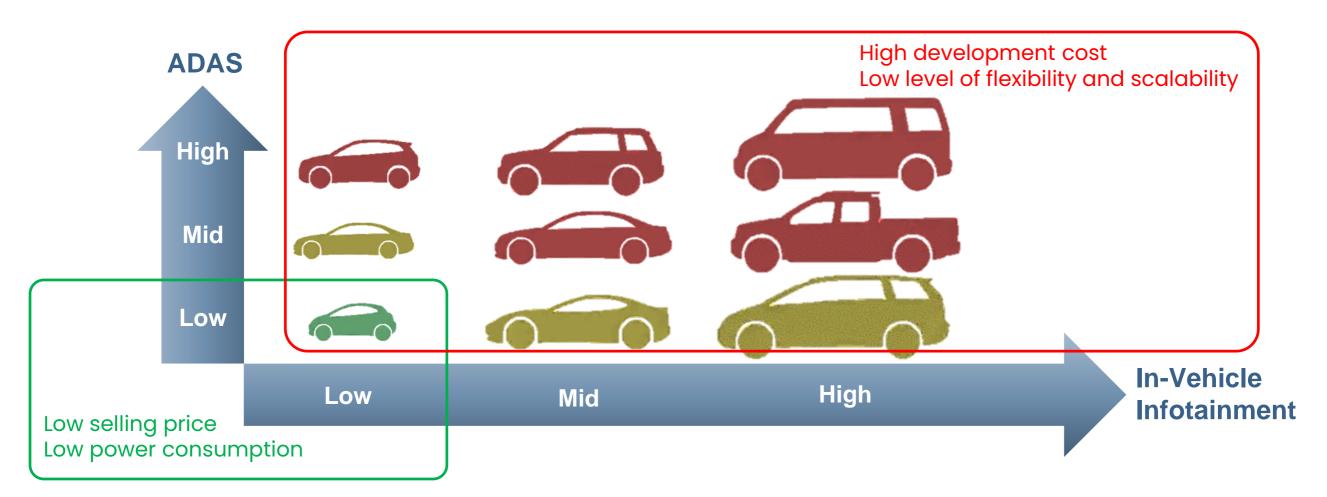

# **GPU** solution

#### One chip covering all segments software defined

<u>cea</u> list

# **ASICs** solution

#### One chip per segment hardware defined

<u>cea</u> list

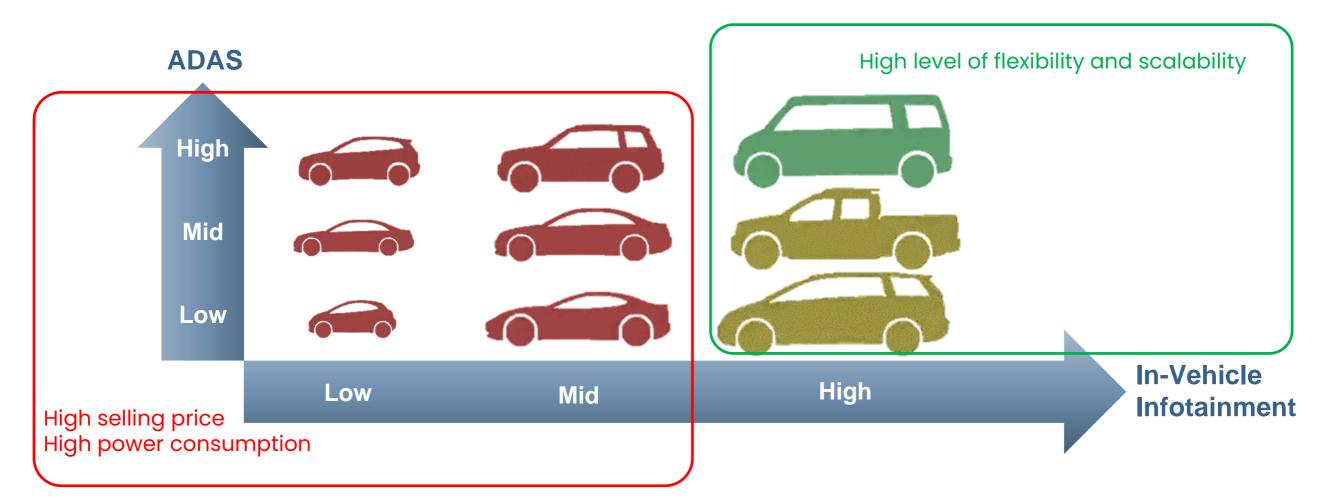

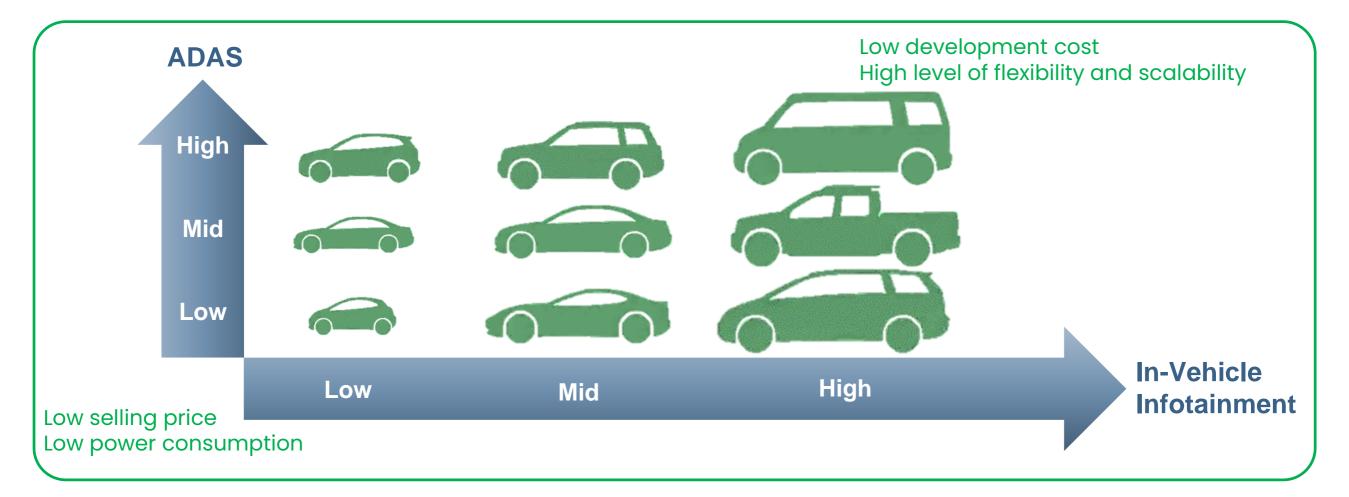

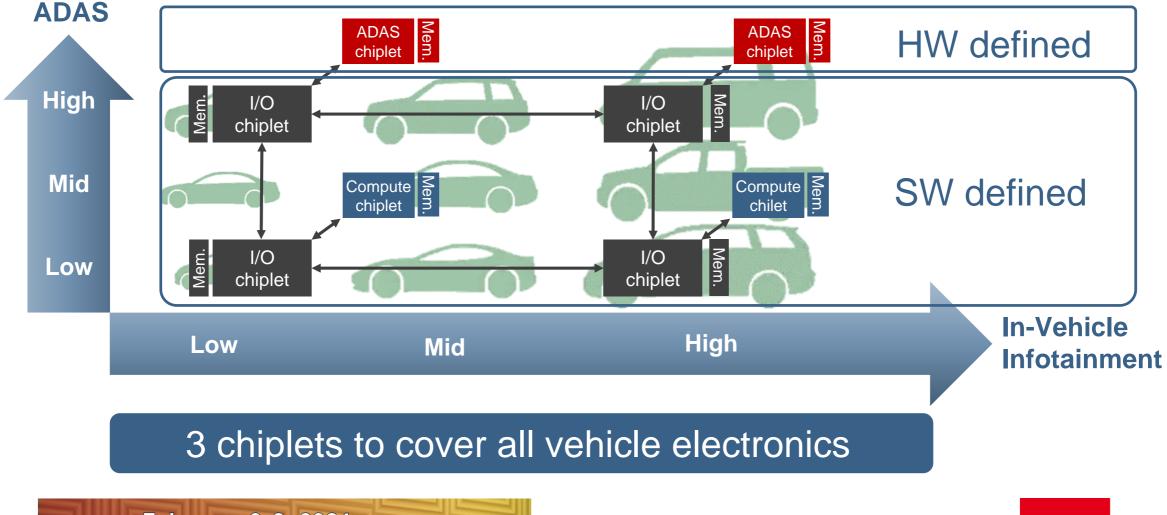

#### Chiplet Solution A few chiplets covering all segments – mix HW and SW defined

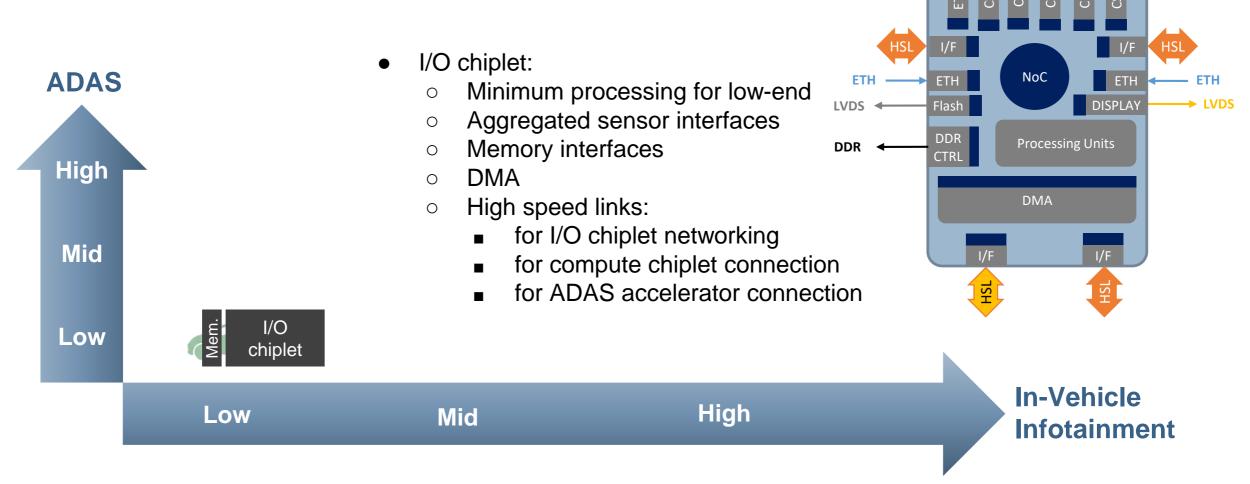

# Chiplet Architecture: I/O chiplet

ETH

LVDS

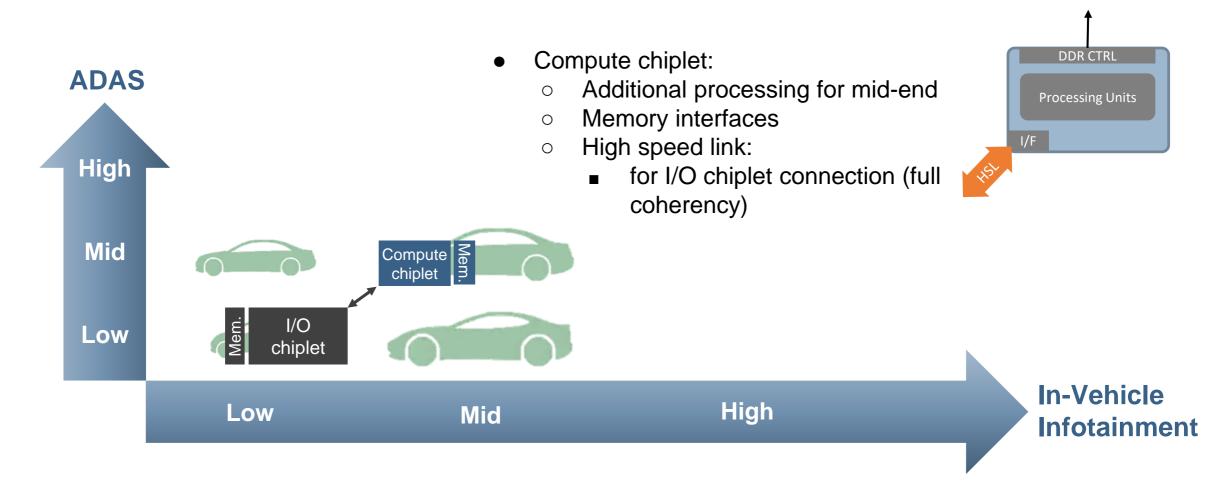

### Chiplet Architecture: compute chiplet

<u>cea</u> list

DDR

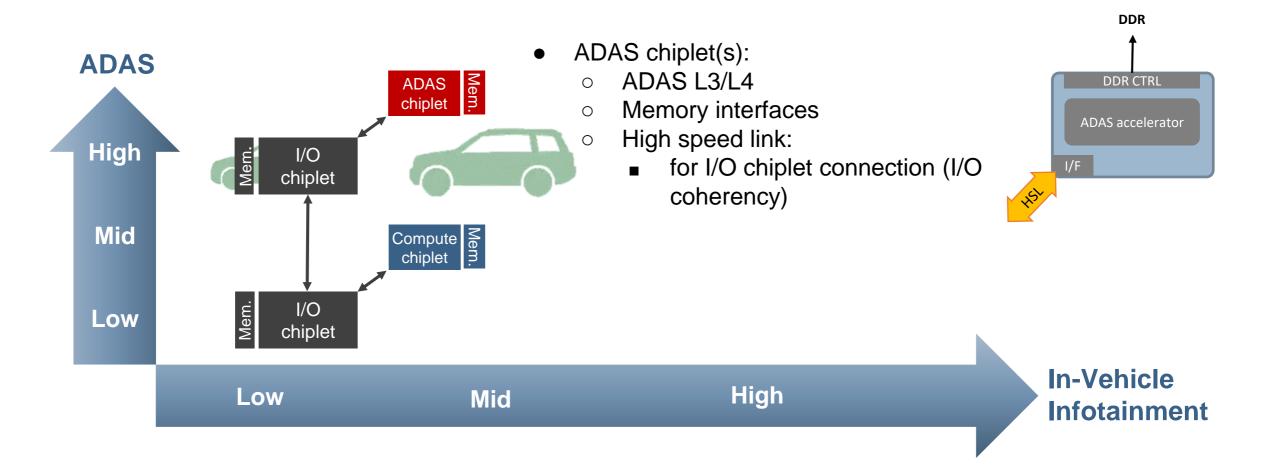

# Chiplet Architecture: ADAS chiplet(s)

<u>cea</u> list

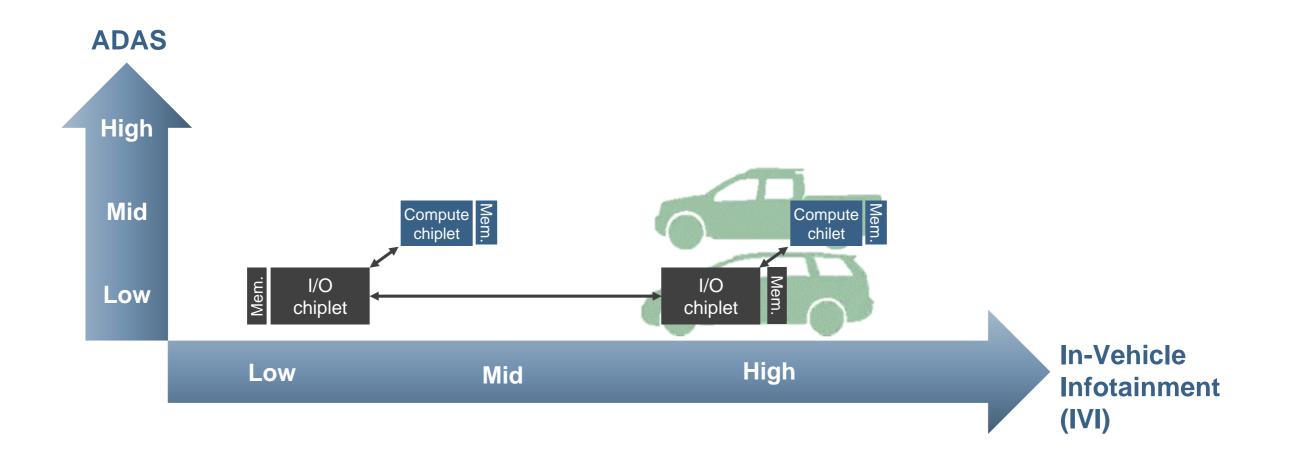

## Chiplet Architecture: scalability towards IVI

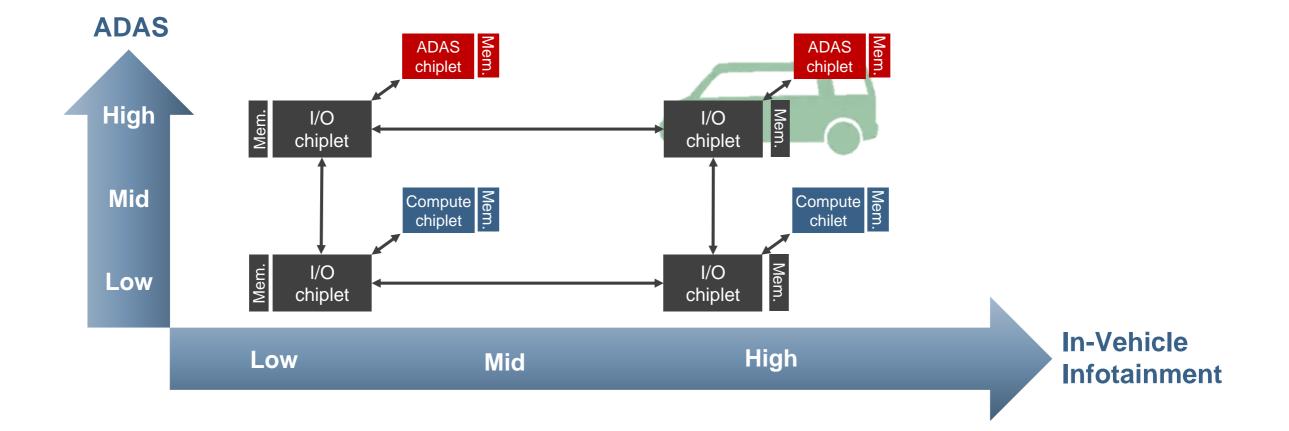

## Chiplet Architecture: scalability towards ADAS

#### Chiplet Architecture A few chiplets covering all segments – mix HW and SW defined

February 6-8, 2024 Santa Clara Convention Center ChipletSummit.com <u>cea</u> list

### Model-Based System Design

February 6-8, 2024 Santa Clara Convention Center ChipletSummit.com <u>cea</u> list

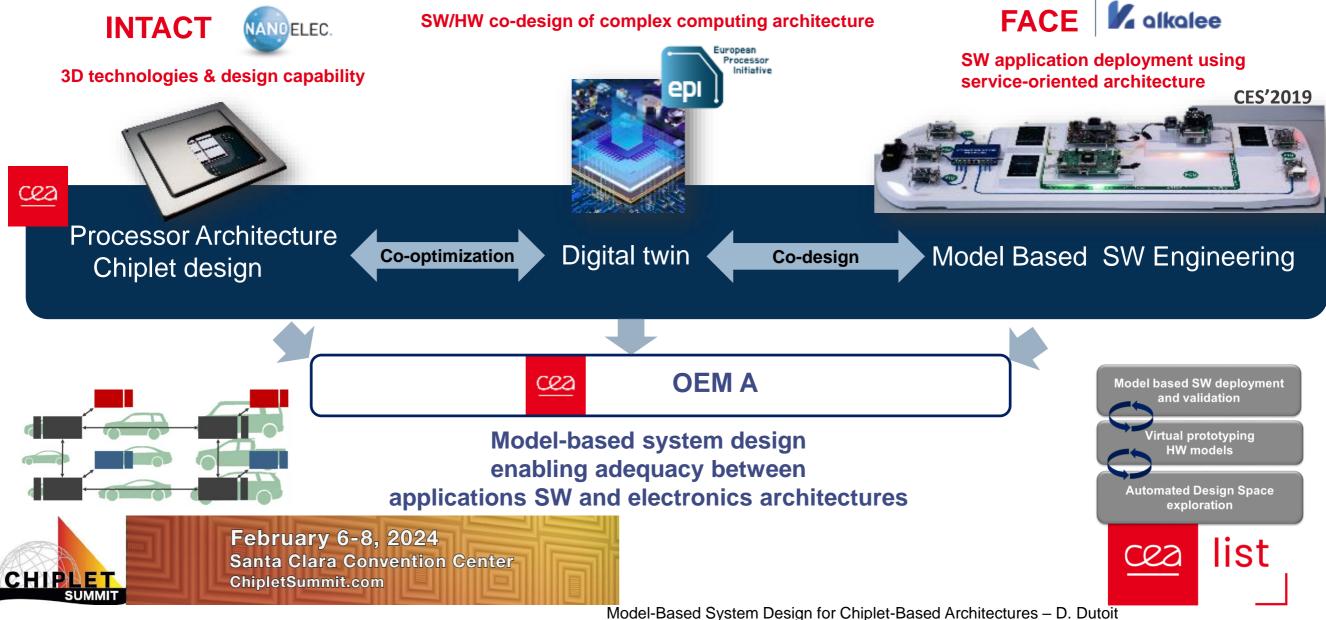

# CEA assets in system design

EPI

cea

#### Processor Architecture Chiplet design

Digital twin

FACE Alkalee

SW application deployment using service-oriented architecture CES'2019

#### Model Based SW Engineering

- World's first 3D System-on-Chip with an active silicon interposer.

- Mary-core architecture (96 cores)

- 3D integrated circuit:

- 6x chiplets in 28nm FDSOI

- 1x active interposer in 65nm

- Full **methodology** of SW/HW **co-design** for general purpose processor specifications

- Delivery to partners of a Virtual Platform of the architecture based on the CEA VPSim tool:

- Performance evaluation of architectural components

- Best compromise accuracy & simulation time

- Formal model of computation and communication

- Model-based software engineering for timing analysis, software deployment on heterogeneous HW, runtime monitoring (safety-critical system)

February 6-8, 2024 Santa Clara Convention Center ChipletSummit.com

# One of the lead projects

EPI

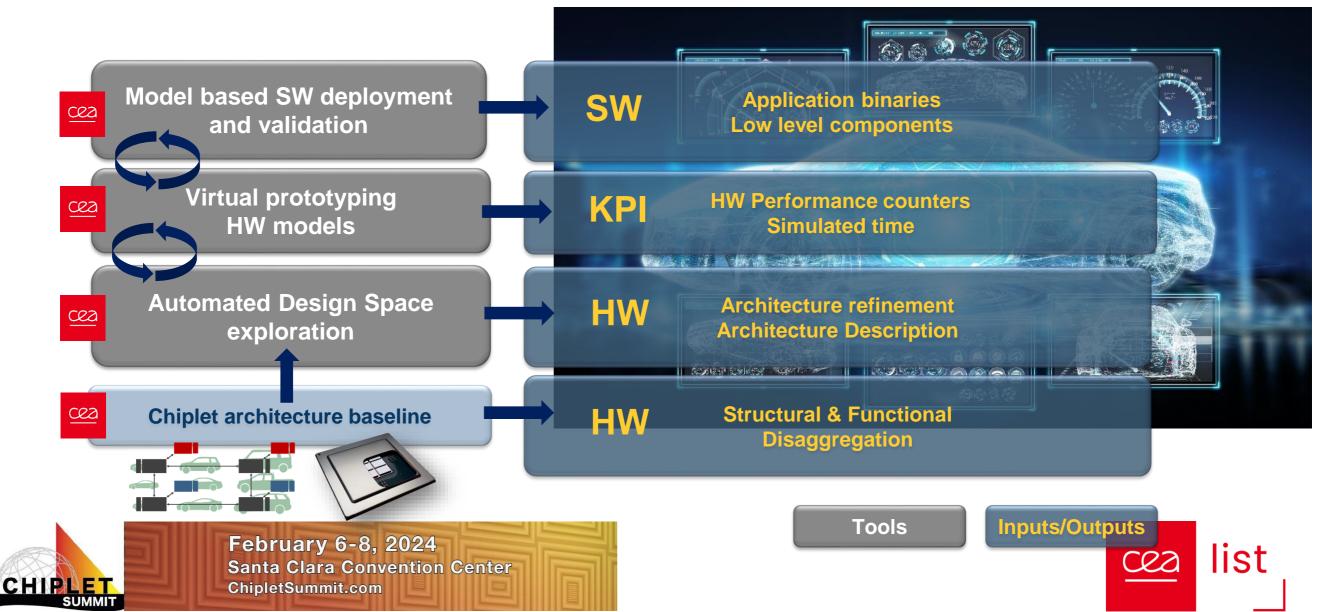

# Model-based system design

Model-Based System Design for Chiplet-Based Architectures – D. Dutoit

24

### Conclusion

- The automotive E/E architecture in moving towards "server on wheels".

- Chiplets are an attractive value proposition for "server on wheels" :

- best trade-off between software-based and hardware-based architecture,

- a few chiplets cover all the needs (in terms of Performance, Power, Area, Cost and Time to market).

- Chiplet-based architectures require system-level design automation based on models:

- virtual prototyping,

- automated design space exploration,

- SW deployment.

Thank you for your attention

Acknowledgements:

- 3D architecture, design & virtual prototype CEA-List teams

- 3D technology CEA-Leti teams

Industrial partners Denis Dutoit – CEA List Program Manager <u>denis.dutoit@cea.fr</u>

#### References

Slide 5:

[VLSI'2013] D. Dutoit et al., "A 0.9 pJ/bit, 12.8 GByte/s WidelO memory interface in a 3D-IC NoC-based MPSoC," 2013 Symposium on VLSI Technology, Kyoto, Japan, 2013, pp. C22-C23.

[ISSCC'2016] P. Vivet et al., "8.1 a 4x4x2 homogeneous scalable 3d network-on-chip circuit with 326mflit/s 0.66pj/b robust and fault-tolerant asynchronous 3d links," 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2016, pp. 146-147, doi: 10.1109/ISSCC.2016.7417949.

[ESSCIRC'2018] E. Guthmuller et al., "A 29 Gops/Watt 3D-Ready 16-Core Computing Fabric with Scalable Cache Coherent Architecture Using Distributed L2 and Adaptive L3 Caches," ESSCIRC 2018 - IEEE 44th European Solid State Circuits Conference (ESSCIRC), Dresden, Germany, 2018, pp. 318-321, doi: 10.1109/ESSCIRC.2018.8494275.

[ISSCC'2020] P. Vivet et al., "2.3 A 220GOPS 96-Core Processor with 6 Chiplets 3D-Stacked on an Active Interposer Offering 0.6ns/mm Latency, 3Tb/s/mm2 Inter-Chiplet Interconnects and 156mW/mm2@ 82%-Peak-Efficiency DC-DC Converters," 2020 IEEE International Solid-State Circuits Conference - (ISSCC), San Francisco, CA, USA, 2020, pp. 46-48, doi: 10.1109/ISSCC19947.2020.9062927.

[VLSI'2020] P. Y. Martinez et al., "ExaNoDe: Combined Integration of Chiplets on Active Interposer with Bare Dice in a Multi-Chip-Module for Heterogeneous and Scalable High Performance Compute Nodes," 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 2020, pp. 1-2, doi: 10.1109/VLSITechnology18217.2020.9265100.

[VLSI'2018] L. Millet et al., "A 5500FPS 85GOPS/W 3D Stacked BSI Vision Chip Based on Parallel in-Focal-Plane Acquisition and Processing," 2018 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 2018, pp. 245-246, doi: 10.1109/VLSIC.2018.8502290.

[VLSI-TSA'2022] P. Vivet et al., "Advanced 3d Design and Technologies for 3-Layer Smart Imager," 2022 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), Hsinchu, Taiwan, 2022, pp. 1-2, doi: 10.1109/VLSI-TSA54299.2022.9771026.

[ISSCC'18] Y. Thonnart et al., "A 10Gb/s Si-photonic transceiver with 150µW 120µs-lock-time digitally supervised analog microring wavelength stabilization for 1Tb/s/mm2 Die-to-Die Optical Networks," 2018 IEEE International Solid-State Circuits Conference - (ISSCC), San Francisco, CA, USA, 2018, pp. 350-352, doi: 10.1109/ISSCC.2018.8310328.

[DATE'2020] Y. Thonnart et al., "POPSTAR: a Robust Modular Optical NoC Architecture for Chiplet-based 3D Integrated Systems," 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 2020, pp. 1456-1461, doi: 10.23919/DATE48585.2020.9116214.